Accurate Small-Signal Modeling of Digitally Controlled Buck Converters with ADC-PWM Synchronization

作者: Hang Zhou, Yuxin Yang, Branislav Hredzak, John Edward Fletcher

分类: eess.SY

发布日期: 2025-10-01 (更新: 2026-01-19)

💡 一句话要点

针对ADC-PWM同步的数字控制Buck变换器,提出精确的小信号建模方法

🎯 匹配领域: 支柱八:物理动画 (Physics-based Animation)

关键词: 数字控制 Buck变换器 小信号建模 ADC-PWM同步 采样数据系统 环路增益 电力电子

📋 核心要点

- 现有数字控制Buck变换器的小信号模型,缺乏对ADC-PWM同步影响的精确建模,导致控制环路设计困难。

- 论文提出了一种基于采样数据框架的精确小信号模型,显式考虑了DPWM-ADC同步,捕捉了采样过程引入的边带效应。

- 通过仿真和实验验证,该模型能够精确预测模拟和数字环路增益,即使在高于开关和采样频率的频率下也是如此。

📝 摘要(中文)

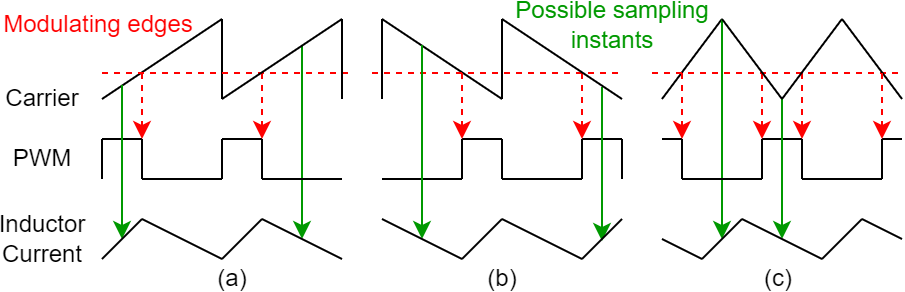

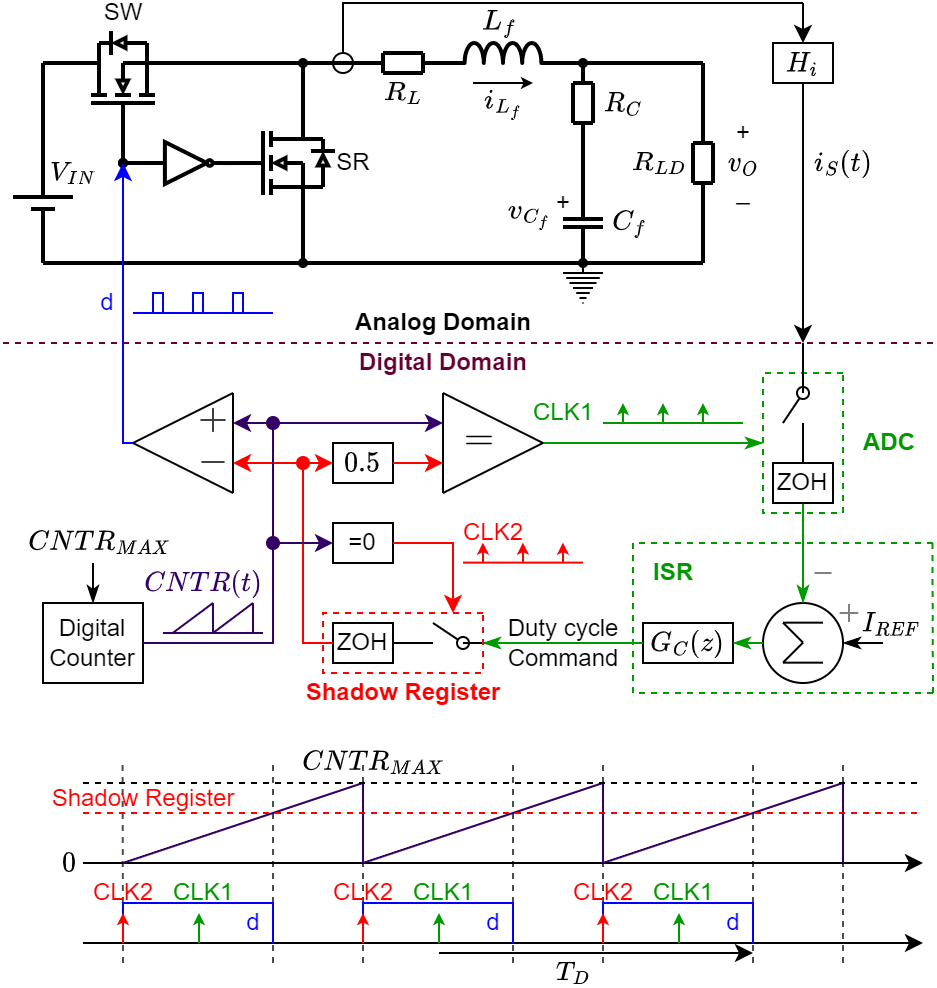

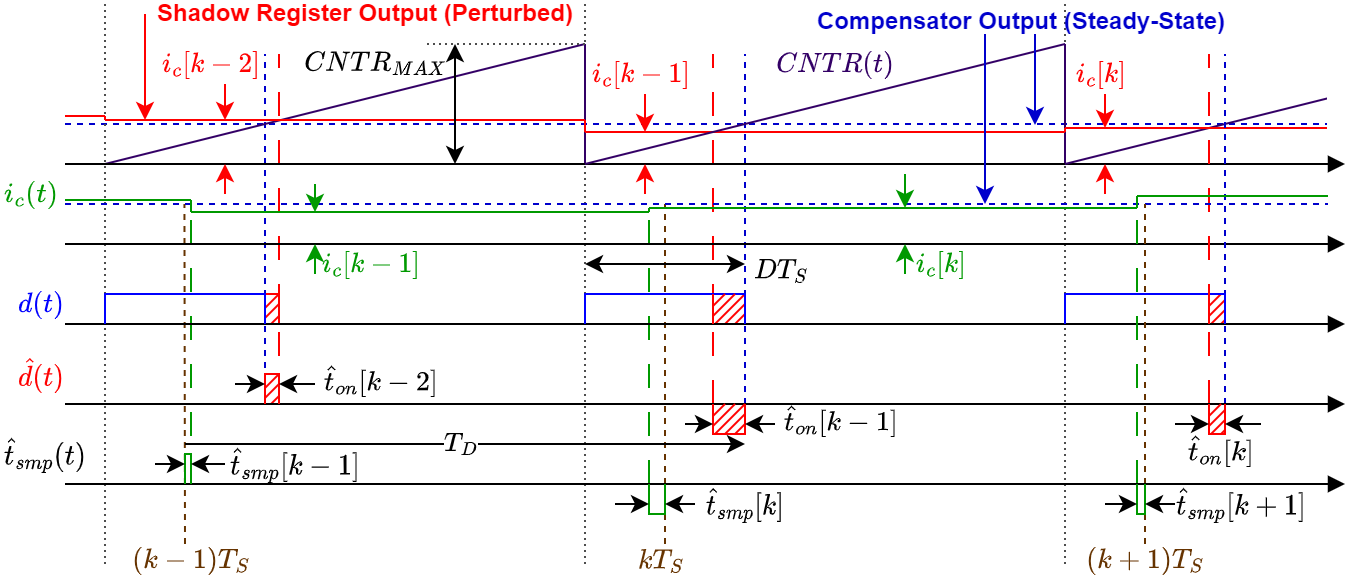

数字控制在现代电力电子变换器中日益普及。在获取电感电流等反馈信号时,通常采用模数转换器(ADC)与数字脉宽调制器(DPWM)同步,以精确跟踪其稳态平均值。然而,这种同步的小信号影响尚未得到研究。本文针对工作在强制连续导通模式(FCCM)下的恒频电流模式控制数字控制Buck变换器,提出了一种精确的小信号模型,显式地考虑了DPWM-ADC同步。利用采样数据框架,该模型捕捉了采样过程引入的所有边带效应,从而能够精确预测模拟和数字环路增益,即使在高于开关和采样频率的频率下也是如此。考虑了非对称和对称载波调制。此外,利用改进的z变换以闭合形式推导了数字环路增益,从而能够进行低复杂度的补偿器设计和稳定性评估。在此框架内,模拟环路增益可以直接从数字环路增益获得,从而消除了对计算密集型无限级数评估的需求。通过仿真和实验结果验证了所提出模型的有效性。

🔬 方法详解

问题定义:现有数字控制Buck变换器的小信号建模,忽略了ADC与DPWM同步带来的影响。这种同步虽然能提高稳态精度,但其对小信号动态特性的影响,特别是环路增益的预测,尚未得到充分研究。因此,现有模型在设计数字补偿器时可能存在偏差,影响系统的稳定性和性能。

核心思路:论文的核心思路是采用采样数据框架,将DPWM-ADC同步过程建模为一个采样系统。通过精确分析采样过程引入的边带效应,建立包含同步影响的小信号模型。该模型能够准确预测模拟和数字环路增益,从而为数字补偿器的设计提供更可靠的依据。

技术框架:该方法首先对数字控制Buck变换器进行建模,包括功率级、DPWM、ADC和数字控制器。然后,利用采样数据理论,将DPWM-ADC同步过程建模为一个采样环节,并分析其对小信号的影响。接着,推导包含同步影响的数字环路增益,并利用改进的z变换将其表示为闭合形式。最后,通过数字环路增益推导出模拟环路增益,避免了复杂的无限级数计算。

关键创新:该论文的关键创新在于显式地考虑了DPWM-ADC同步对数字控制Buck变换器小信号特性的影响。通过采样数据框架,精确建模了同步过程引入的边带效应,从而能够更准确地预测环路增益。此外,利用改进的z变换,将数字环路增益表示为闭合形式,大大简化了补偿器的设计和稳定性分析。与现有方法相比,该方法能够提供更精确的小信号模型,提高数字控制系统的性能和可靠性。

关键设计:论文的关键设计包括:1) 采用采样数据框架对DPWM-ADC同步过程进行建模;2) 推导包含同步影响的数字环路增益,并利用改进的z变换将其表示为闭合形式;3) 通过数字环路增益推导出模拟环路增益,避免了复杂的无限级数计算。此外,论文还考虑了非对称和对称载波调制两种情况,并针对恒频电流模式控制进行了优化。

🖼️ 关键图片

📊 实验亮点

论文通过仿真和实验验证了所提出模型的有效性。实验结果表明,该模型能够精确预测模拟和数字环路增益,即使在高于开关和采样频率的频率下也是如此。与忽略DPWM-ADC同步影响的传统模型相比,该模型能够更准确地预测系统的稳定性和动态特性,从而为数字补偿器的设计提供更可靠的依据。具体性能提升数据未知。

🎯 应用场景

该研究成果可广泛应用于各种采用数字控制的电力电子变换器,如DC-DC变换器、AC-DC变换器和逆变器等。精确的小信号模型能够提高数字控制系统的设计效率和性能,从而提升电源的功率密度、效率和可靠性。尤其在对动态性能要求较高的应用场景,如服务器电源、通信电源和电动汽车充电器等,该研究具有重要的实际价值。

📄 摘要(原文)

Digital control has become increasingly widespread in modern power electronic converters. When acquiring feedback signals such as the inductor current, synchronizing the analog-to-digital converter (ADC) with the digital pulse-width modulator (DPWM) is commonly employed to accurately track their steady-state average. However, the small-signal implications of such synchronization have not been investigated. This paper presents an exact small-signal model for digitally controlled buck converters operating in forced continuous-conduction mode (FCCM) under constant-frequency current-mode control, explicitly accounting for DPWM-ADC synchronization. Using a sampled-data framework, the proposed model captures all sideband effects introduced by the sampling process, yielding precise predictions of both analog and digital loop gains, even at frequencies beyond the switching and sampling frequencies. Both asymmetrical and symmetrical carrier modulations are considered. Furthermore, the digital loop gain is derived in closed form using the modified z-transform, enabling low-complexity compensator design and stability assessment. Within this framework, the analog loop gain can be directly obtained from the digital loop gain, thereby eliminating the need for computationally intensive infinite series evaluations. The validity of the proposed model is confirmed through both simulation and experimental results.