Design-Agnostic Distributed Timing Fault Injection Monitor With End-to-End Design Automation

作者: Yan He, Yumin Su, Kaiyuan Yang

分类: eess.SY

发布日期: 2025-01-16

备注: 12 pages, 26 figures

期刊: IEEE Journal of Solid-State Circuits, 04 December 2024

DOI: 10.1109/JSSC.2024.3504546

💡 一句话要点

提出一种与设计无关的分布式时序故障注入监测器,并实现端到端设计自动化

🎯 匹配领域: 支柱八:物理动画 (Physics-based Animation)

关键词: 时序故障注入攻击 硬件安全 故障检测 延迟锁定环 设计自动化

📋 核心要点

- 现有系统易受低成本时序故障注入攻击,攻击者通过篡改时钟信号或芯片工作条件即可发起攻击。

- 提出一种可综合、可分布的原位故障注入监测器,利用锁相环跟踪时钟脉冲宽度,检测时序故障。

- 该设计在65nm CMOS工艺下验证,面积小,可检测多种时钟毛刺和时序故障注入,频率范围广。

📝 摘要(中文)

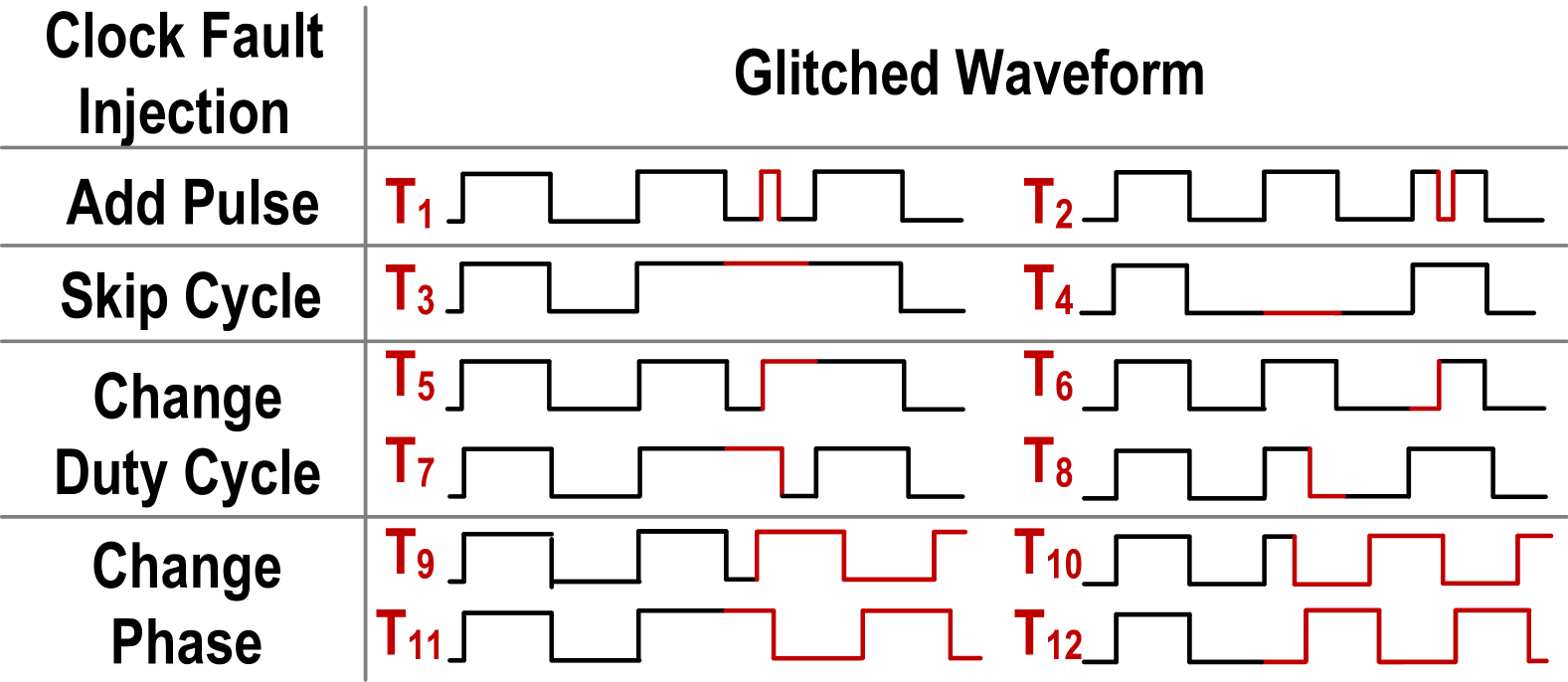

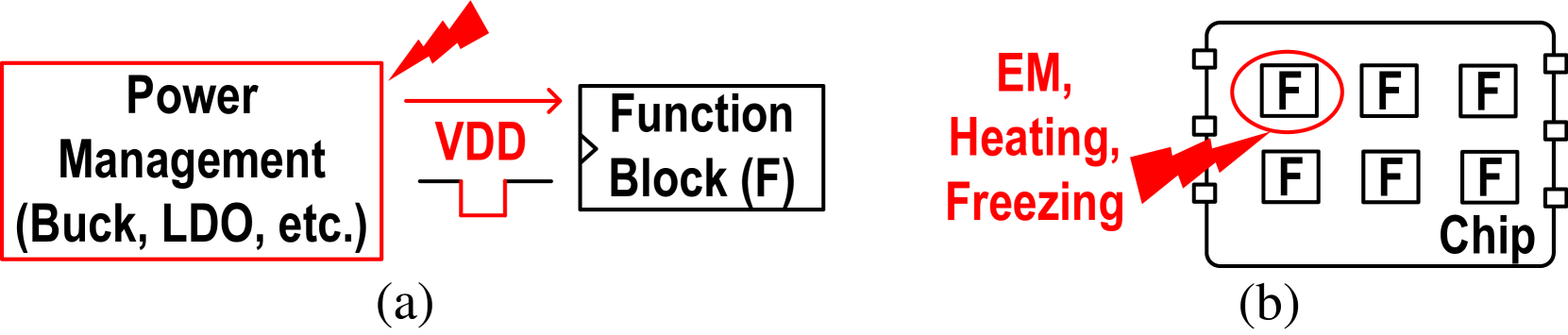

故障注入攻击(FIA)通过在电路中诱导硬件故障并利用这些故障来危害系统安全。已证实,FIA可以绕过系统安全机制,导致错误的输出,并获取秘密信息。某些类型的FIA可以通过篡改时钟信号或芯片工作条件轻松实现。为了缓解这种低成本但功能强大的攻击,我们提出了一种完全可综合且可分布的原位故障注入监测器,该监测器采用锁相环来跟踪时钟的脉冲宽度。我们进一步开发了一个完全自动化的设计框架,以优化和实现在任何工艺节点上的FIA监测器。我们的设计采用65纳米CMOS技术制造和验证,占地面积小,仅为1500平方微米。它可以锁定2 MHz至1.26 GHz的时钟频率,同时检测所有12种可能的时钟毛刺,以及通过电源电压、电磁信号和芯片温度进行的时序FIA注入。

🔬 方法详解

问题定义:论文旨在解决硬件电路中时序故障注入攻击(FIA)的问题。现有的安全机制难以有效防御通过篡改时钟信号、电源电压、电磁信号或芯片温度等方式进行的时序FIA。这些攻击成本低,但危害大,可能导致系统安全漏洞和信息泄露。

核心思路:论文的核心思路是设计一种原位(in situ)的、分布式的时序故障注入监测器,该监测器能够实时监测时钟信号的异常变化,从而检测到FIA的发生。通过将监测器分布在电路的关键位置,可以提高检测的覆盖率和响应速度。

技术框架:该监测器的整体架构包括一个延迟锁定环(DLL)和一个故障检测模块。DLL用于跟踪时钟信号的脉冲宽度,并生成一个参考信号。故障检测模块将实际的时钟信号与参考信号进行比较,如果两者之间的差异超过预设的阈值,则认为发生了故障注入。此外,论文还开发了一个全自动化的设计框架,用于优化和实现FIA监测器。

关键创新:该论文的关键创新在于提出了一种与设计无关的(design-agnostic)的监测器设计方法。这意味着该监测器可以应用于不同的电路设计,而无需进行大量的定制化修改。此外,该监测器还具有可分布性,可以根据需要将其部署在电路的不同位置。全自动化的设计框架也大大简化了监测器的设计和实现过程。

关键设计:DLL的设计是关键。DLL需要能够快速锁定到时钟信号,并具有较高的精度。故障检测模块需要能够区分正常的时钟抖动和由FIA引起的异常变化。阈值的设置需要根据具体的应用场景进行调整,以避免误报或漏报。此外,监测器的功耗和面积也是重要的设计考虑因素。

🖼️ 关键图片

📊 实验亮点

该设计在65nm CMOS工艺下进行了验证,面积仅为1500平方微米,功耗低。实验结果表明,该监测器可以锁定2 MHz至1.26 GHz的时钟频率,并能检测所有12种可能的时钟毛刺。此外,该监测器还能有效检测通过电源电压、电磁信号和芯片温度进行的时序FIA注入。与现有方法相比,该监测器具有更高的检测精度和更低的功耗。

🎯 应用场景

该研究成果可广泛应用于对安全性要求较高的电子系统中,例如金融系统、军事系统、航空航天系统等。通过在这些系统中部署该故障注入监测器,可以有效地检测和防御时序故障注入攻击,提高系统的安全性和可靠性。此外,该技术还可以用于硬件安全评估和漏洞分析,帮助开发人员发现和修复潜在的安全漏洞。未来,该技术有望成为硬件安全领域的重要组成部分。

📄 摘要(原文)

Fault injection attacks induce hardware failures in circuits and exploit these faults to compromise the security of the system. It has been demonstrated that FIAs can bypass system security mechanisms, cause faulty outputs, and gain access to secret information. Certain types of FIAs can be mounted with little effort by tampering with clock signals and or the chip operating conditions. To mitigate such low cost, yet powerful attacks, we propose a fully synthesizable and distributable in situ fault injection monitor that employs a delay locked loop to track the pulsewidth of the clock. We further develop a fully automated design framework to optimize and implement the FIA monitors at any process node. Our design is fabricated and verified in 65 nm CMOS technology with a small footprint of 1500 um2. It can lock to clock frequencies from 2 MHz to 1.26 GHz while detecting all 12 types of possible clock glitches, as well as timing FIA injections via the supply voltage, electromagnetic signals, and chip temperature.