A Time Optimization Framework for the Implementation of Robust and Low-latency Quantum Circuits

作者: Eduardo Willwock Lussi, Rafael de Santiago, Eduardo Inacio Duzzioni

分类: quant-ph, eess.SY

发布日期: 2024-12-24

备注: 12 pages

期刊: Phys. Rev. Applied 23, 044036 (2025)

DOI: 10.1103/PhysRevApplied.23.044036

💡 一句话要点

提出一种时间优化框架,在量子电路中融合快速门和鲁棒门以提升性能。

🎯 匹配领域: 支柱八:物理动画 (Physics-based Animation)

关键词: 量子计算 量子电路优化 时间优化 鲁棒量子门 快速量子门 脉冲调度 依赖图

📋 核心要点

- 量子电路易受退相干影响,缩短了计算时间,而快速量子门虽能减少延迟,但易导致泄漏,优化空间受限。

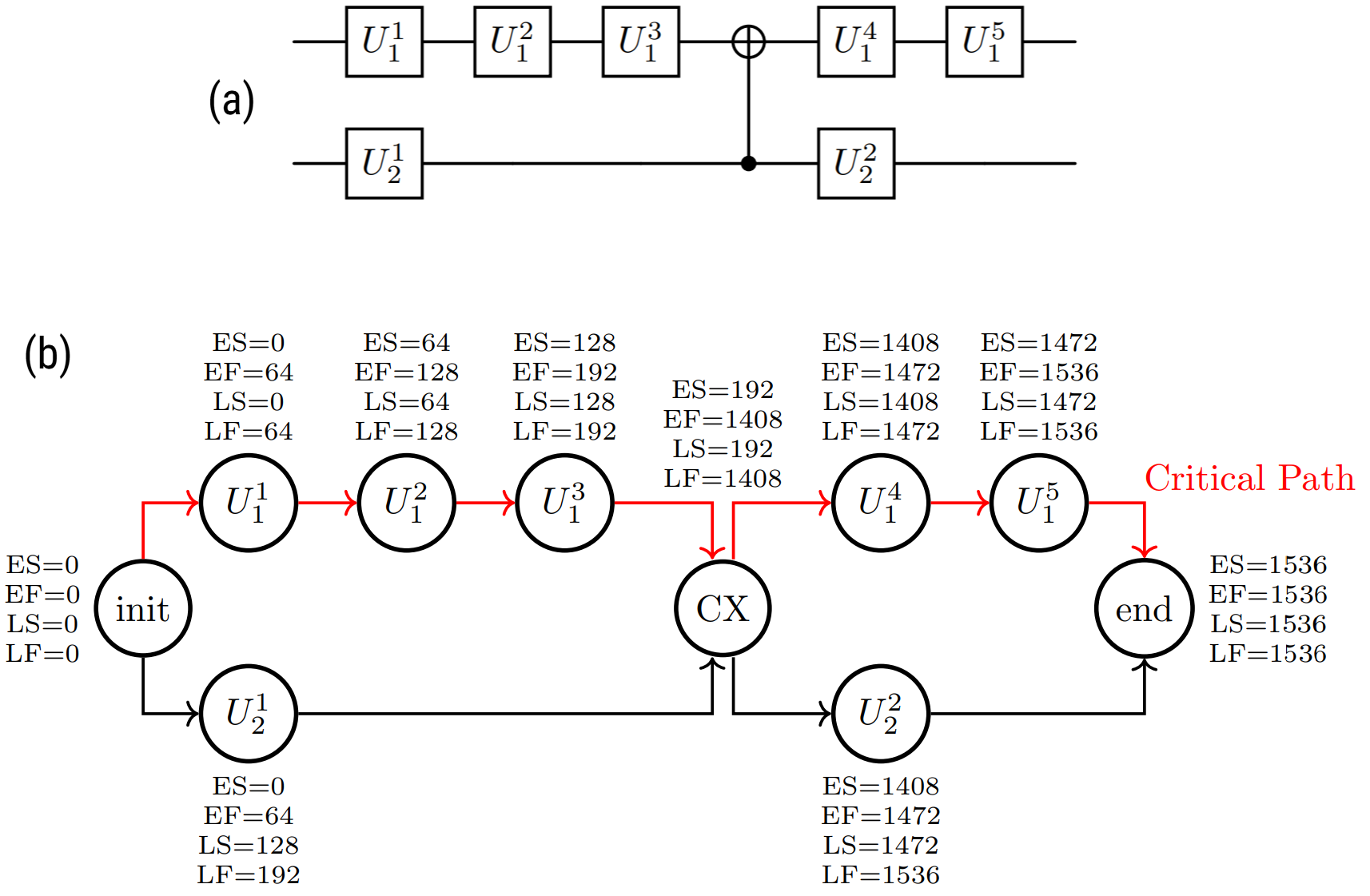

- 该论文提出一种时间优化框架,通过依赖图建模量子电路,在关键路径上使用快速门,非关键路径使用鲁棒门。

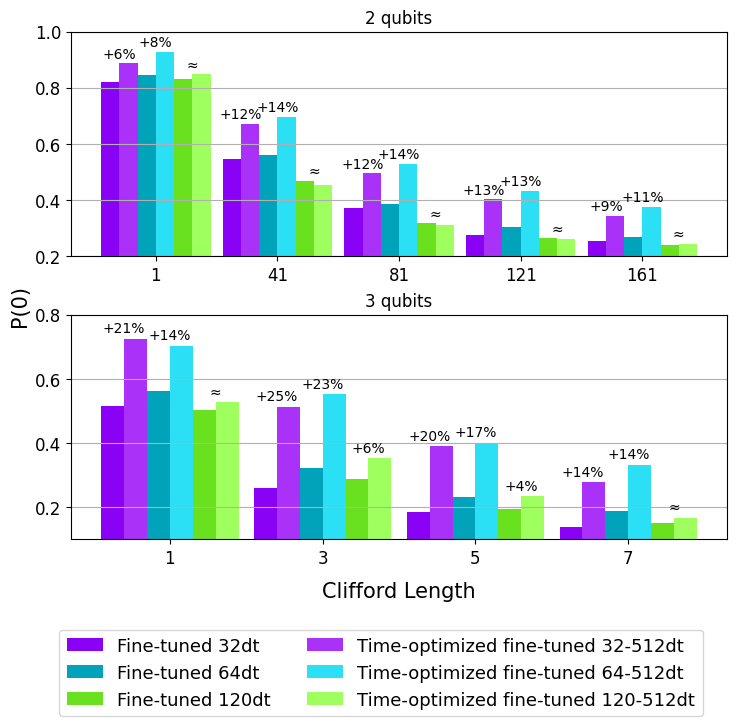

- 实验结果表明,该方法在IBMQ Brisbane上将量子电路成功概率提升超过25%,且性能增益随量子比特数增加而扩展。

📝 摘要(中文)

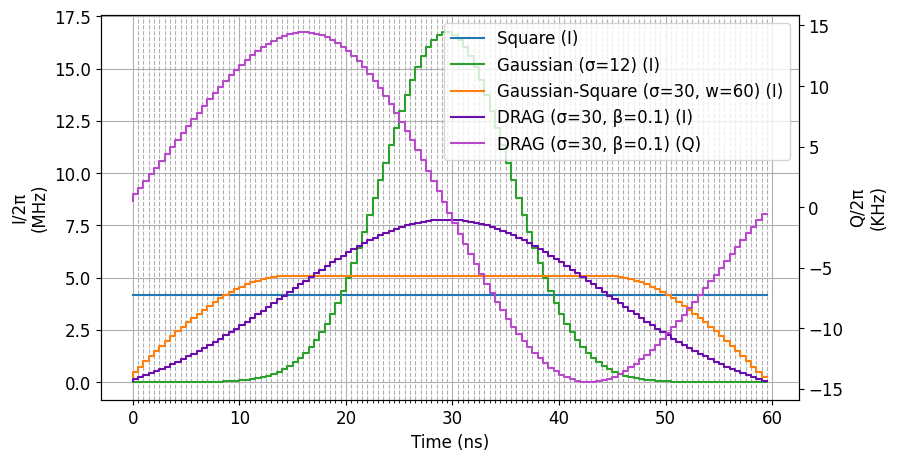

量子计算在解决复杂计算问题方面展现出巨大潜力。然而,在量子硬件中实现有意义的可扩展性和噪声控制仍然面临挑战。退相干引起的非相干误差限制了总计算时间。虽然硬件不断进步,但量子软件专家也在努力最小化量子电路延迟以减轻耗散。然而,在脉冲级别,快速量子门通常会导致泄漏,优化空间有限。量子控制技术在生成对相干误差源具有鲁棒性的量子门方面显示出有效性,但代价是门持续时间延长。本文提出了一种替代的脉冲调度方法,可以在同一量子电路中同时使用快速量子门和鲁棒量子门。该时间优化框架将量子电路建模为依赖图,在关键路径上实现最快的量子门,并利用关键路径之外的空闲时间,从门集中优化实现更长、更鲁棒的门,而不会增加延迟。在IBMQ Brisbane上进行的实验表明,该方法将量子电路执行的绝对成功概率提高了25%以上,并且性能增益随着量子比特数量的增加而扩展。

🔬 方法详解

问题定义:量子计算面临的主要挑战是在存在噪声的情况下,如何高效地执行量子电路。现有的方法要么侧重于使用快速但易出错的量子门,要么使用鲁棒但耗时的量子门。快速门容易受到泄漏的影响,而鲁棒门会增加电路的整体延迟,从而限制了量子计算的保真度。因此,需要在速度和鲁棒性之间找到一个平衡点。

核心思路:该论文的核心思路是根据量子电路中不同门的重要性,自适应地选择使用快速门或鲁棒门。关键路径上的门对整体延迟影响最大,因此使用快速门来最小化延迟。非关键路径上的门则可以使用更鲁棒的门,以提高电路的整体保真度。这种方法旨在充分利用量子硬件的空闲时间,在不增加延迟的情况下提高电路的鲁棒性。

技术框架:该时间优化框架主要包含以下几个阶段:1. 依赖图构建:将量子电路表示为一个依赖图,其中节点表示量子门,边表示门之间的依赖关系。2. 关键路径识别:使用图算法识别电路中的关键路径,即影响电路整体延迟的最长路径。3. 门选择与调度:在关键路径上选择最快的量子门,而在非关键路径上选择更鲁棒的量子门。利用空闲时间优化鲁棒门的实现,避免增加整体延迟。4. 电路执行与验证:在量子硬件上执行优化后的量子电路,并评估其性能。

关键创新:该论文的关键创新在于提出了一种混合使用快速门和鲁棒门的脉冲调度方法。与传统方法不同,该方法不是简单地选择一种类型的门,而是根据门在电路中的位置和重要性,自适应地选择合适的门。这种方法能够在延迟和鲁棒性之间实现更好的平衡,从而提高量子电路的整体性能。

关键设计:该框架的关键设计包括:1. 依赖图的构建方式:如何准确地表示量子门之间的依赖关系,以便有效地识别关键路径。2. 门选择策略:如何根据门的类型、位置和硬件特性,选择合适的快速门或鲁棒门。3. 时间优化算法:如何利用空闲时间优化鲁棒门的实现,避免增加整体延迟。具体的参数设置和损失函数等技术细节在论文中未详细说明,属于未知信息。

🖼️ 关键图片

📊 实验亮点

实验结果表明,该时间优化框架在IBMQ Brisbane上将量子电路执行的绝对成功概率提高了25%以上。此外,性能增益随着量子比特数量的增加而扩展,表明该方法具有良好的可扩展性。这些结果验证了该方法在提高量子电路性能方面的有效性。

🎯 应用场景

该研究成果可应用于各种量子算法的优化,尤其是在对计算时间敏感的应用场景中,例如量子模拟、量子机器学习和量子优化等。通过提高量子电路的保真度和降低延迟,该方法有望加速量子计算在实际问题中的应用,并推动量子计算技术的发展。

📄 摘要(原文)

Quantum computing has garnered attention for its potential to solve complex computational problems with considerable speedup. Despite notable advancements in the field, achieving meaningful scalability and noise control in quantum hardware remains challenging. Incoherent errors caused by decoherence restrict the total computation time, making it very short. While hardware advancements continue to progress, quantum software specialists seek to minimize quantum circuit latency to mitigate dissipation. However, at the pulse level, fast quantum gates often lead to leakage, leaving minimal room for further optimization. Recent advancements have shown the effectiveness of quantum control techniques in generating quantum gates robust to coherent error sources. Nevertheless, these techniques come with a trade-off -- extended gate durations. In this paper, we introduce an alternative pulse scheduling approach that enables the use of both fast and robust quantum gates within the same quantum circuit. The time-optimization framework models the quantum circuit as a dependency graph, implements the fastest quantum gates on the critical path, and uses idle periods outside the critical path to optimally implement longer, more robust gates from the gate set, without increasing latency. Experiments conducted on IBMQ Brisbane show that this approach improves the absolute success probability of quantum circuit execution by more than 25%, with performance gains scaling as the number of qubits increases.