Low-Power Encoding for PAM-3 DRAM Bus

作者: Jonghyeon Nam, Jaeduk Han, Hokeun Kim

分类: eess.SY, cs.AR

发布日期: 2024-10-16

备注: To appear in Proceedings of the 20th International Conference on Synthesis, Modeling, Analysis and Simulation Methods, and Applications to Circuit Design (SMACD 2024)

💡 一句话要点

针对PAM-3 DRAM总线,提出低功耗编码算法以降低高速内存链路的功耗

🎯 匹配领域: 支柱八:物理动画 (Physics-based Animation)

关键词: PAM-3 DRAM总线 低功耗编码 内存接口 能量效率

📋 核心要点

- 现有高速内存接口功耗高,尤其是在终端电阻上的功耗,成为性能瓶颈。

- 论文提出PAM3-DBI、PAM3-MF和PAM3-SORT三种低功耗编码算法,旨在降低PAM-3 DRAM总线的功耗。

- 实验结果表明,提出的编码算法能够显著降低高速内存链路的终端功耗,降幅高达41%至90%。

📝 摘要(中文)

本文针对内存接口中日益普及的三电平脉冲幅度调制(PAM-3)信号,提出三种低功耗数据编码算法:PAM3-DBI、PAM3-MF和PAM3-SORT。相较于PAM-4,PAM-3具有更大的电压裕量。为了最大化PAM-3的优势,我们利用gem5计算机架构模拟器运行基准测试,并使用DRAM内存trace评估了这三种PAM-3编码技术的能量效率。实验结果表明,所提出的算法能够显著降低高速内存链路的终端功耗,对于基准测试程序,降幅可达41%至90%。

🔬 方法详解

问题定义:论文旨在解决高速DRAM总线中,由于采用PAM-3调制技术带来的高功耗问题。特别是在终端电阻上的功耗,严重影响了内存系统的整体能效。现有的编码方案可能无法充分利用PAM-3的特性来优化功耗,因此需要新的低功耗编码策略。

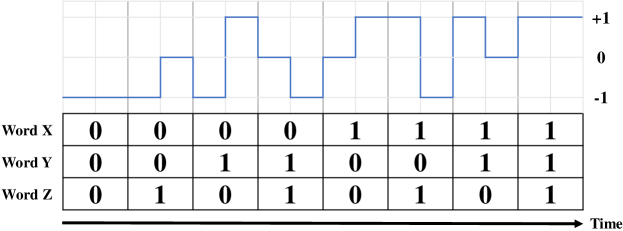

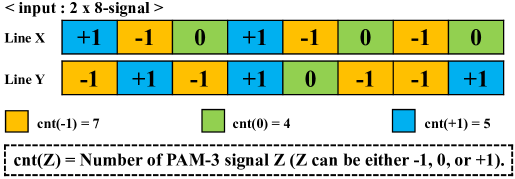

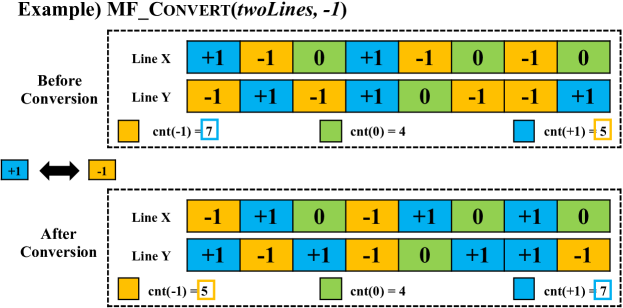

核心思路:论文的核心思路是通过设计特定的数据编码算法,减少PAM-3信号在传输过程中的电平转换次数和幅度变化,从而降低终端电阻上的功耗。不同的编码算法侧重于不同的优化目标,例如最小化电平转换、优化信号频率分布等。

技术框架:论文的技术框架主要包括三个部分:首先,分析PAM-3信号的特性和功耗模型;其次,设计三种不同的低功耗编码算法(PAM3-DBI、PAM3-MF和PAM3-SORT);最后,通过gem5模拟器运行基准测试,并使用DRAM内存trace来评估这些编码算法的能量效率。

关键创新:论文的关键创新在于提出了三种针对PAM-3 DRAM总线的低功耗编码算法。这些算法并非简单地将现有的编码方案应用于PAM-3,而是充分考虑了PAM-3信号的特性,并针对性地设计了优化策略。例如,PAM3-DBI可能类似于数据总线反转,PAM3-MF可能关注信号频率的优化,PAM3-SORT可能关注信号幅度的排序。具体细节未知,需要查阅原文。

关键设计:由于论文细节未知,无法给出具体的参数设置、损失函数或网络结构等技术细节。但可以推测,关键设计可能包括:编码算法的具体实现方式(例如,如何选择反转哪些数据位),编码算法的复杂度分析(确保编码和解码过程不会引入过多的延迟),以及针对不同应用场景选择合适的编码算法的策略。

🖼️ 关键图片

📊 实验亮点

实验结果表明,提出的三种PAM-3编码算法能够显著降低高速内存链路的终端功耗。对于基准测试程序,功耗降幅可达41%至90%。这一结果表明,所提出的编码算法在降低DRAM总线功耗方面具有显著优势,能够有效提高内存系统的能量效率。

🎯 应用场景

该研究成果可应用于各种需要高速低功耗内存的电子设备中,例如高性能计算机、服务器、移动设备和嵌入式系统。通过降低DRAM总线的功耗,可以延长电池续航时间、提高系统性能和降低散热需求,具有重要的实际应用价值和广泛的应用前景。

📄 摘要(原文)

The 3-level pulse amplitude modulation (PAM-3) signaling is expected to be widely used in memory interfaces for its greater voltage margins compared to PAM-4. To maximize the benefit of PAM-3, we propose three low-power data encoding algorithms: PAM3-DBI, PAM3-MF, and PAM3-SORT. With the DRAM memory traces from the gem5 computer architecture simulator running benchmarks, we evaluate the energy efficiency of our three PAM-3 encoding techniques. The experimental results show the proposed algorithms can reduce termination power for high-speed memory links significantly by 41% to 90% for benchmark programs.