Characterizing and Optimizing Real-Time Optimal Control for Embedded SoCs

作者: Kris Shengjun Dong, Dima Nikiforov, Widyadewi Soedarmadji, Minh Nguyen, Vikram Jain, Christopher W. Fletcher, Yakun Sophia Shao

分类: cs.RO, eess.SY

发布日期: 2024-10-16 (更新: 2025-10-09)

💡 一句话要点

针对嵌入式SoC,探索并优化实时最优控制算法的硬件架构

🎯 匹配领域: 支柱一:机器人控制 (Robot Control)

关键词: 模型预测控制 硬件加速 嵌入式系统 RISC-V 机器人 代码生成 软硬件协同优化

📋 核心要点

- 资源受限的机器人难以高效执行计算密集型任务,特别是实时模型预测控制(MPC)等算法。

- 通过探索CPU、向量处理器和专用加速器等多种硬件架构,寻找最优的MPC算法硬件实现方案。

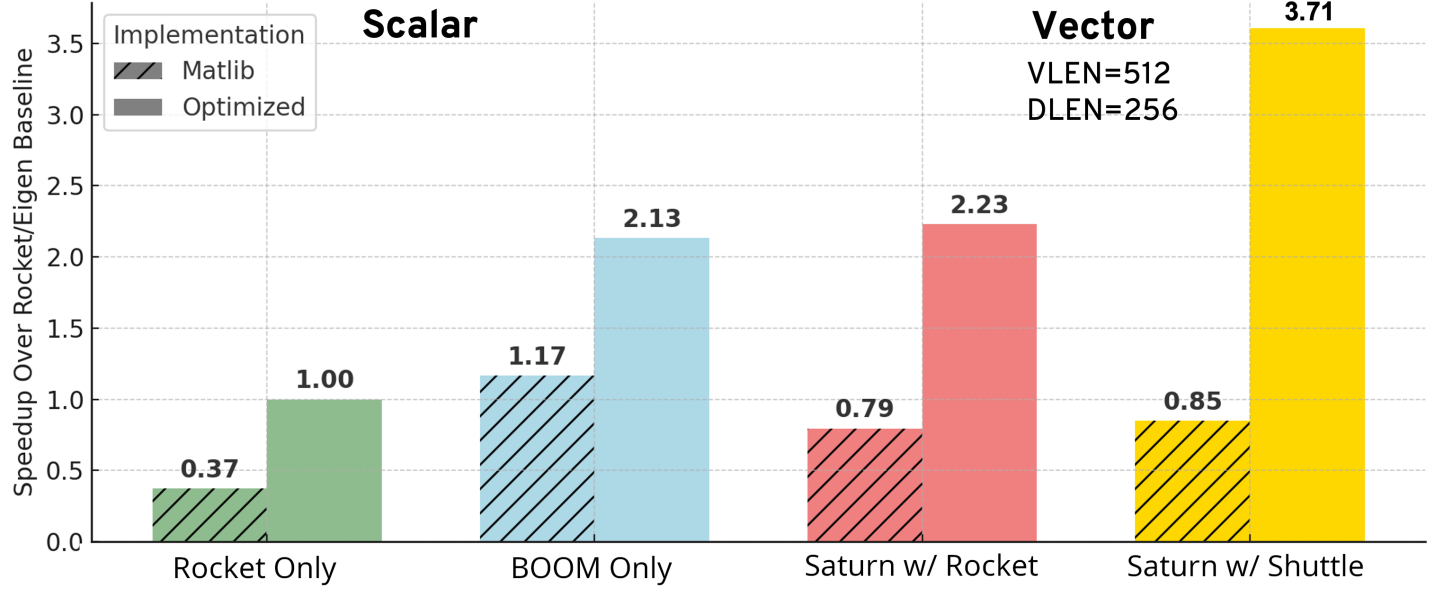

- 实验结果表明,架构优化和软硬件协同优化可使MPC加速3.71倍,系统功耗降低27%。

📝 摘要(中文)

资源受限的机器人面临执行计算密集型任务的重大挑战,例如运动和操作,特别是对于实时最优控制算法,如模型预测控制(MPC)。本文提供了一个全面的设计空间探索,以确定这些高要求的基于模型的控制算法的最佳硬件计算架构。我们分析并优化了具有代表性的架构设计,包括通用标量CPU、向量处理器和专用加速器。通过表征内核级基准测试和端到端机器人场景,包括在已制造的RISC-V多核向量SoC上的硬件在环评估,我们对不同架构设计点的性能、面积和利用率进行了定量比较。我们的研究结果表明,有针对性的架构修改,加上深度软件和系统优化,能够使MPC加速高达3.71倍,从而在完成机器人任务的同时,系统级功耗降低高达27%。最后,我们提出了一种代码生成流程,旨在简化将机器人工作负载映射到专用架构所需的复杂工程工作。

🔬 方法详解

问题定义:论文旨在解决资源受限的嵌入式系统中,实时最优控制算法(特别是模型预测控制MPC)计算量大,难以高效执行的问题。现有方法在通用处理器上的性能不足,而专用硬件加速器的设计又过于复杂,缺乏通用性和灵活性。

核心思路:论文的核心思路是通过全面的设计空间探索,找到针对MPC算法的最佳硬件架构。这包括对不同类型的处理器(CPU、向量处理器、专用加速器)进行性能分析和优化,并结合软硬件协同优化,以在性能、功耗和面积之间取得平衡。

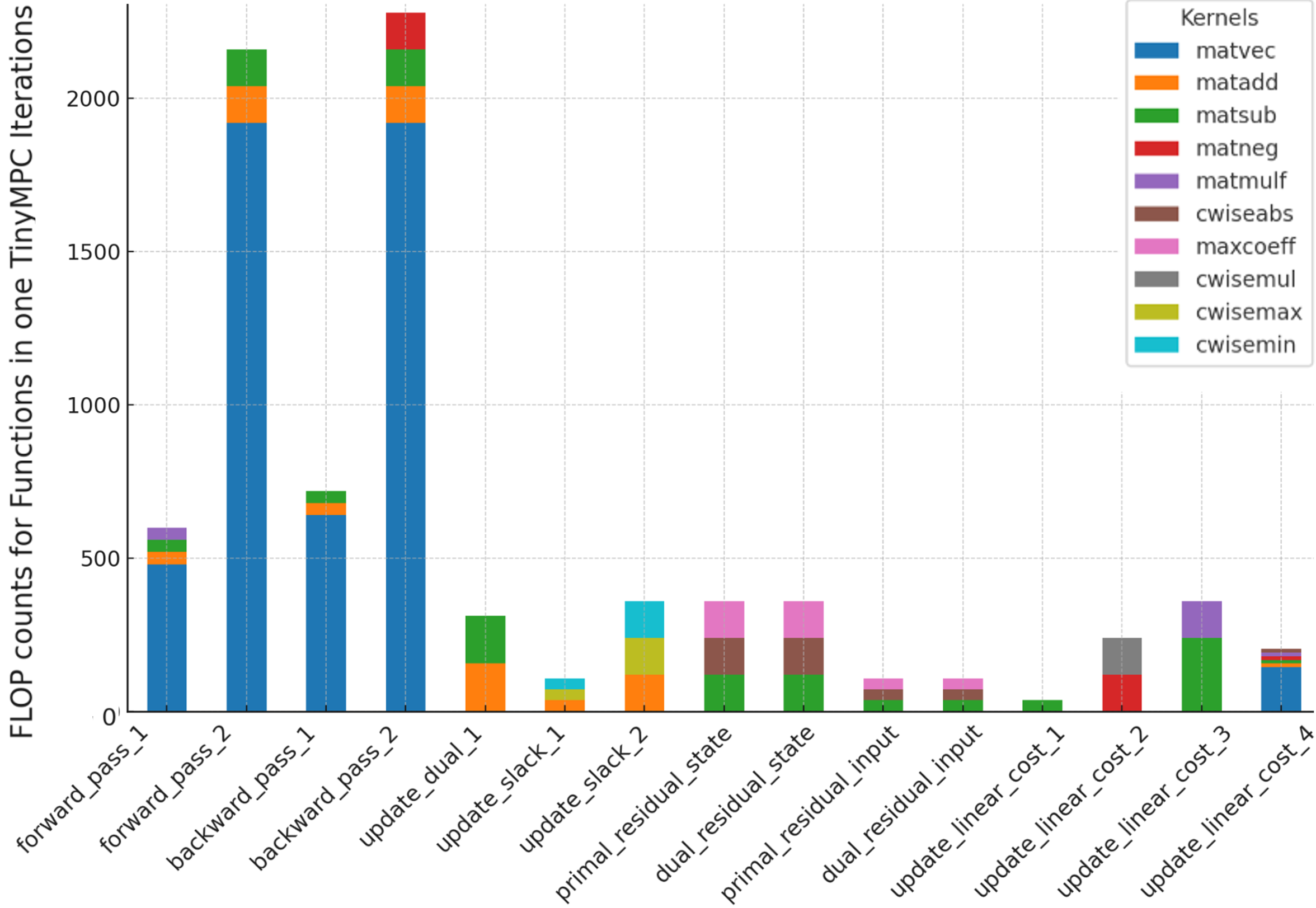

技术框架:论文的技术框架主要包括以下几个阶段:1) 对MPC算法进行内核级基准测试,分析计算瓶颈;2) 探索不同的硬件架构设计,包括通用CPU、向量处理器和专用加速器;3) 对选定的架构进行软件和系统优化,例如代码优化、内存管理优化等;4) 在RISC-V多核向量SoC上进行硬件在环评估,验证优化效果;5) 提出一种代码生成流程,简化机器人工作负载到专用架构的映射。

关键创新:论文的关键创新在于:1) 对不同硬件架构在执行MPC算法时的性能进行了全面的定量比较,为硬件选择提供了依据;2) 提出了软硬件协同优化方法,显著提高了MPC算法的执行效率;3) 设计了一种代码生成流程,降低了将机器人工作负载映射到专用架构的复杂性。

关键设计:论文的关键设计包括:1) 针对MPC算法的特点,对向量处理器的指令集进行了优化;2) 设计了一种高效的内存访问模式,减少了数据传输的开销;3) 采用硬件在环仿真,对系统进行实时性能评估和验证;4) 代码生成流程能够自动将高层次的机器人控制算法转换为针对特定硬件架构的优化代码。

🖼️ 关键图片

📊 实验亮点

实验结果表明,通过有针对性的架构修改以及深度软硬件协同优化,MPC算法的执行速度提升了3.71倍,同时系统级功耗降低了27%。硬件在环评估验证了优化后的系统在实际机器人任务中的有效性。此外,论文提出的代码生成流程显著简化了将机器人工作负载映射到专用架构的过程。

🎯 应用场景

该研究成果可广泛应用于资源受限的机器人领域,例如无人机、移动机器人、机械臂等。通过优化硬件架构和软件算法,可以提高机器人的运动控制性能和自主决策能力,使其能够执行更复杂的任务。此外,该研究提出的代码生成流程可以降低机器人软件开发的门槛,加速机器人技术的普及。

📄 摘要(原文)

Resource-limited robots face significant challenges in executing computationally intensive tasks, such as locomotion and manipulation, particularly for real-time optimal control algorithms like Model Predictive Control (MPC). This paper provides a comprehensive design space exploration to identify optimal hardware computation architectures for these demanding model-based control algorithms. We profile and optimize representative architectural designs, including general-purpose scalar CPUs, vector processors, and specialized accelerators. By characterizing kernel-level benchmarks and end-to-end robotic scenarios, including a hardware-in-the-loop evaluation on a fabricated RISC-V multi-core vector SoC, we present a quantitative comparison of performance, area, and utilization across distinct architectural design points. Our findings demonstrate that targeted architectural modifications, coupled with deep software and system optimizations, enable up to 3.71x speedups for MPC, resulting in up to 27% system-level power reductions while completing robotic tasks. Finally, we propose a code generation flow designed to simplify the complex engineering effort required for mapping robotic workloads onto specialized architectures.