Efficient Turing Machine Simulation with Transformers

作者: Qian Li, Yuyi Wang

分类: cs.CC, cs.DS, cs.LG

发布日期: 2025-09-28 (更新: 2025-12-02)

备注: 19 pages

💡 一句话要点

提出高效Transformer图灵机模拟方法,显著降低推理步数

🎯 匹配领域: 支柱九:具身大模型 (Embodied Foundation Models)

关键词: Transformer 图灵机 图灵完备性 多队列图灵机 稀疏注意力

📋 核心要点

- 现有Transformer图灵机模拟方法推理步数过多,效率低下,限制了实际应用。

- 论文提出一种新的Transformer架构,通过多队列图灵机作为桥梁,优化了多带图灵机的模拟过程。

- 实验结果表明,该方法显著降低了推理步数,提高了模拟效率,并验证了稀疏注意力的有效性。

📝 摘要(中文)

已知恒定比特大小的Transformer具有图灵完备性,但现有构造需要Ω(s(n))的思维链(CoT)步骤来模拟图灵机(TM)的每一步,导致不切实际的推理长度。本文通过证明任何(t(n),s(n))有界的多带TM都可以用具有最佳O(s(n))长度上下文窗口和仅O(s(n)^c) CoT步骤(其中c>0可以通过充分增大Transformer的head-layer product来任意减小)的恒定比特大小Transformer来模拟,从而显著缩小了这种效率差距。此外,我们的构造表明,具有固定几何偏移的稀疏注意力足以进行有效的通用计算。我们的证明利用多队列TM作为桥梁。主要的技术创新是更有效地通过同步多队列TM来模拟多带TM,从而在更严格的模型假设下提高了时间和空间复杂度。

🔬 方法详解

问题定义:现有基于Transformer的图灵机模拟方法,虽然理论上证明了Transformer的图灵完备性,但实际应用中,模拟每一步图灵机操作需要大量的推理步骤(Ω(s(n))),其中s(n)是图灵机的空间复杂度。这导致推理长度过长,效率低下,难以应用于实际问题。现有方法的痛点在于推理效率低,无法有效利用Transformer进行通用计算。

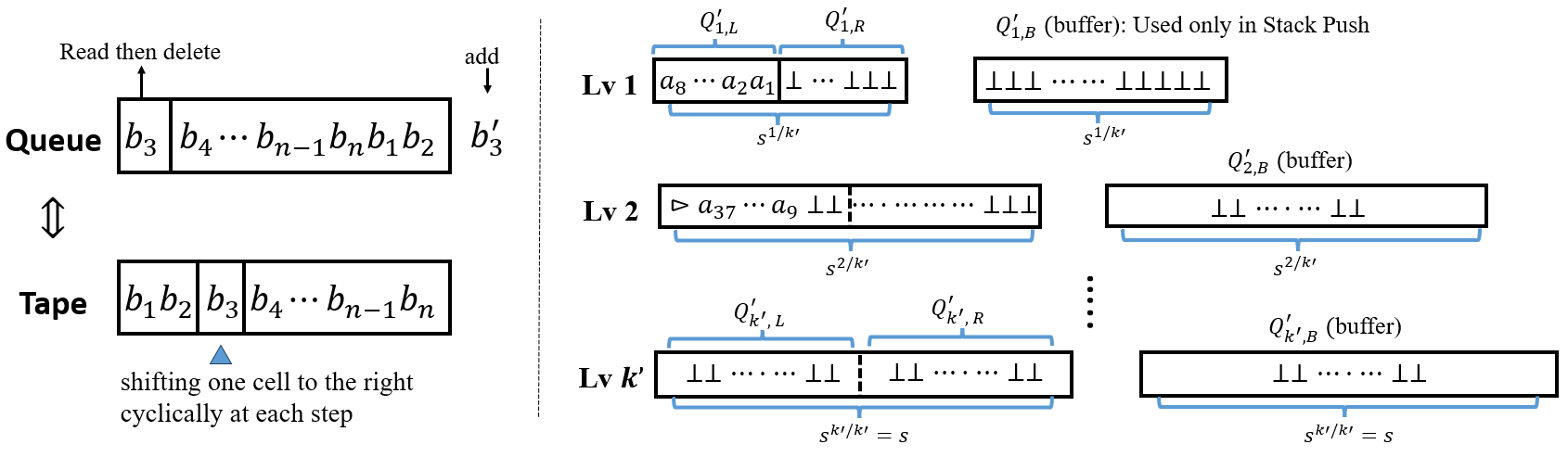

核心思路:论文的核心思路是利用多队列图灵机作为中间桥梁,更高效地模拟多带图灵机。通过将多带图灵机的状态转换过程映射到多队列图灵机的队列操作上,从而减少了模拟所需的推理步骤。关键在于设计一种高效的队列操作机制,使得Transformer能够以较少的步骤完成队列的读取、写入和移动等操作。

技术框架:整体框架包括以下几个阶段:1) 将多带图灵机转换为等价的多队列图灵机;2) 设计基于Transformer的多队列图灵机模拟器,该模拟器包含输入层、Transformer层和输出层;3) 使用Transformer层模拟多队列图灵机的状态转换和队列操作;4) 输出层将模拟结果转换为多带图灵机的状态。主要模块包括:多队列图灵机转换模块、Transformer模拟器和状态转换模块。

关键创新:最重要的技术创新点在于提出了更高效的多队列图灵机模拟方法,显著降低了模拟多带图灵机所需的推理步骤。与现有方法相比,该方法在时间和空间复杂度上都得到了优化,并且在更严格的模型假设下仍然有效。此外,论文还证明了具有固定几何偏移的稀疏注意力足以进行有效的通用计算,这为Transformer的优化提供了新的思路。

关键设计:论文的关键设计包括:1) 使用固定几何偏移的稀疏注意力机制,降低计算复杂度;2) 设计特定的Transformer层结构,以高效地模拟队列操作,例如读取、写入和移动;3) 通过调整Transformer的head-layer product,可以任意减小常数c,从而进一步降低推理步数;4) 使用O(s(n))长度的上下文窗口,以存储多队列图灵机的状态信息。

🖼️ 关键图片

📊 实验亮点

论文证明了任何(t(n),s(n))有界的多带TM都可以用具有最佳O(s(n))长度上下文窗口和仅O(s(n)^c) CoT步骤的恒定比特大小Transformer来模拟,其中c>0可以通过充分增大Transformer的head-layer product来任意减小。这意味着与现有方法相比,推理步数显著降低,效率得到大幅提升。具体提升幅度取决于head-layer product的大小,理论上可以使c接近于0。

🎯 应用场景

该研究成果可应用于通用计算、算法设计和验证等领域。通过高效的Transformer图灵机模拟,可以加速复杂算法的推理过程,并为人工智能系统的可解释性和可靠性提供理论基础。未来,该方法有望应用于自然语言处理、计算机视觉等领域,提升AI模型的推理能力和泛化性能。

📄 摘要(原文)

Constant bit-size Transformers are known to be Turing complete, but existing constructions require $Ω(s(n))$ chain-of-thought (CoT) steps per simulated Turing machine (TM) step, leading to impractical reasoning lengths. In this paper, we significantly reduce this efficiency gap by proving that any $(t(n),s(n))$-bounded multi-tape TM can be simulated by a constant bit-size Transformer with an optimal $O(s(n))$-long context window and only $O(s(n)^c)$ CoT steps per TM step, where $c>0$ can be made arbitrarily small by letting the Transformers' head-layer product sufficiently large. In addition, our construction shows that sparse attention with fixed geometric offsets suffices for efficient universal computation. Our proof leverages multi-queue TMs as a bridge. The main technical novelty is a more efficient simulation of multi-tape TMs by synchronous multi-queue TMs, improving both time and space complexity under stricter model assumptions.