FedBit: Accelerating Privacy-Preserving Federated Learning via Bit-Interleaved Packing and Cross-Layer Co-Design

作者: Xiangchen Meng, Yangdi Lyu

分类: cs.CR, cs.AR, cs.LG

发布日期: 2025-09-27

💡 一句话要点

FedBit:通过比特交织打包和跨层协同设计加速隐私保护联邦学习

🎯 匹配领域: 支柱五:交互与反应 (Interaction & Reaction)

关键词: 联邦学习 同态加密 FPGA加速 隐私保护 比特交织 软硬件协同设计

📋 核心要点

- 同态加密联邦学习虽能保护数据隐私,但其计算负担和密文扩展显著增加了资源和通信开销。

- FedBit采用比特交织数据打包,将多个模型参数嵌入单个密文系数,减少密文扩展并提升计算并行性。

- FedBit集成了FPGA加速器和优化数据流,实验表明其加密速度提升两个数量级,通信开销降低60.7%。

📝 摘要(中文)

本文提出FedBit,一个为Brakerski-Fan-Vercauteren (BFV)方案优化的硬件/软件协同设计框架,旨在加速隐私保护联邦学习。FedBit通过比特交织数据打包将多个模型参数嵌入到单个密文系数中,从而最小化密文扩展并最大化计算并行性。此外,FedBit集成了一个专用FPGA加速器来处理密码学操作,并采用优化的数据流来降低内存开销。实验结果表明,FedBit在加密方面实现了两个数量级的加速,并将平均通信开销降低了60.7%,同时保持了较高的准确率。

🔬 方法详解

问题定义:在联邦学习中,使用同态加密(FHE)保护模型更新的隐私性会引入巨大的计算开销和通信开销。现有的方法在加密和传输过程中效率较低,导致训练速度慢,资源消耗大,难以在实际场景中应用。尤其是在资源受限的边缘设备上,这个问题更加突出。

核心思路:FedBit的核心思路是通过软硬件协同设计来优化同态加密过程。具体来说,通过比特交织打包技术减少密文扩展,提高计算并行性;利用FPGA加速器加速密码学运算,并优化数据流以降低内存开销。这种协同设计旨在充分利用硬件加速的优势,同时优化软件层面的数据处理,从而实现整体性能的提升。

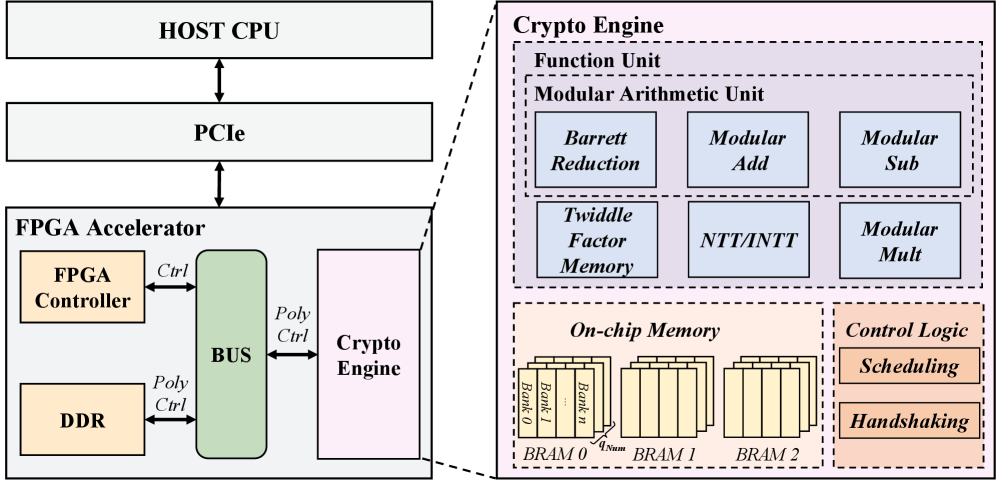

技术框架:FedBit的整体框架包括以下几个主要模块:1) 比特交织打包模块:将多个模型参数打包到单个密文系数中。2) FPGA加速器:负责执行同态加密相关的计算密集型操作,如多项式乘法和模约简。3) 优化数据流:设计高效的数据传输和存储方案,减少内存访问开销。4) 软件控制层:负责协调各个模块的工作,并提供易于使用的API。

关键创新:FedBit的关键创新在于比特交织打包技术和软硬件协同设计。比特交织打包能够有效地减少密文扩展,提高计算效率。软硬件协同设计则能够充分利用硬件加速的优势,同时优化软件层面的数据处理,从而实现整体性能的提升。与现有方法相比,FedBit更加注重软硬件之间的协同优化,从而在计算效率和通信开销方面取得了显著的提升。

关键设计:在比特交织打包方面,需要仔细选择打包的参数数量和比特位数,以平衡计算效率和精度损失。FPGA加速器的设计需要根据BFV方案的特点进行优化,例如,采用高度并行的架构来加速多项式乘法。数据流的设计需要考虑内存带宽的限制,尽量减少不必要的数据传输。此外,还需要对BFV方案的参数进行调整,以适应硬件加速器的特性。

🖼️ 关键图片

📊 实验亮点

FedBit的实验结果表明,其在加密速度上实现了两个数量级的提升,与传统方法相比,平均通信开销降低了60.7%。同时,FedBit在保持较高模型准确率的前提下,显著降低了计算和通信开销,验证了其在隐私保护联邦学习中的有效性。这些结果表明,FedBit能够有效地加速联邦学习过程,并降低资源消耗。

🎯 应用场景

FedBit在需要保护用户数据隐私的联邦学习场景中具有广泛的应用前景,例如医疗健康、金融服务和自动驾驶等领域。它可以帮助在保护数据隐私的前提下,实现跨机构或设备的数据共享和模型训练,从而提升模型的性能和泛化能力。此外,FedBit还可以应用于边缘计算场景,例如智能摄像头和物联网设备,在本地进行模型训练和推理,从而降低延迟和带宽需求。

📄 摘要(原文)

Federated learning (FL) with fully homomorphic encryption (FHE) effectively safeguards data privacy during model aggregation by encrypting local model updates before transmission, mitigating threats from untrusted servers or eavesdroppers in transmission. However, the computational burden and ciphertext expansion associated with homomorphic encryption can significantly increase resource and communication overhead. To address these challenges, we propose FedBit, a hardware/software co-designed framework optimized for the Brakerski-Fan-Vercauteren (BFV) scheme. FedBit employs bit-interleaved data packing to embed multiple model parameters into a single ciphertext coefficient, thereby minimizing ciphertext expansion and maximizing computational parallelism. Additionally, we integrate a dedicated FPGA accelerator to handle cryptographic operations and an optimized dataflow to reduce the memory overhead. Experimental results demonstrate that FedBit achieves a speedup of two orders of magnitude in encryption and lowers average communication overhead by 60.7%, while maintaining high accuracy.