HiVeGen -- Hierarchical LLM-based Verilog Generation for Scalable Chip Design

作者: Jinwei Tang, Jiayin Qin, Kiran Thorat, Chen Zhu-Tian, Yu Cao, Yang, Zhao, Caiwen Ding

分类: cs.LG, cs.AI, cs.AR

发布日期: 2024-12-06 (更新: 2025-10-09)

💡 一句话要点

HiVeGen:一种基于分层LLM的可扩展芯片设计Verilog生成框架

🎯 匹配领域: 支柱九:具身大模型 (Embodied Foundation Models)

关键词: 硬件描述语言生成 大型语言模型 分层设计 设计空间探索 领域专用加速器

📋 核心要点

- 现有LLM在硬件描述语言生成方面存在局限,难以生成复杂硬件的分层结构,导致代码幻觉问题。

- HiVeGen通过将Verilog生成任务分解为LLM可管理的分层子模块,有效降低了生成复杂性。

- HiVeGen集成了自动设计空间探索、代码重用机制和人机交互,显著提升了生成代码的质量。

📝 摘要(中文)

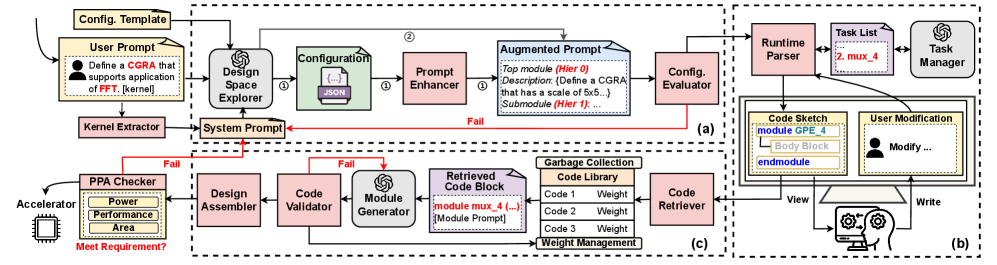

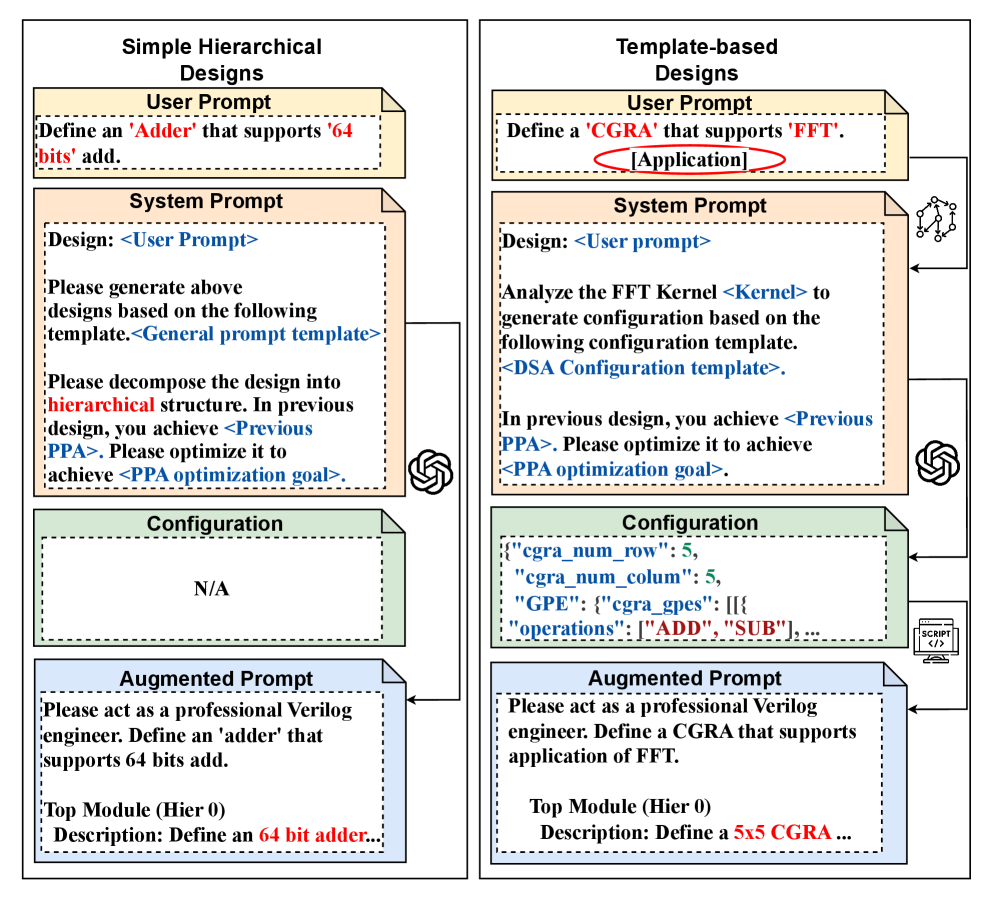

随着大型语言模型(LLMs)最近在代码生成方面表现出令人印象深刻的能力,将其能力扩展到硬件描述语言(HDL)是很有前景的。然而,LLMs倾向于生成单个HDL代码块,而不是用于硬件设计的分层结构,这导致幻觉,尤其是在像特定领域加速器(DSAs)这样的复杂设计中。为了解决这个问题,我们提出了HiVeGen,一个基于分层LLM的Verilog生成框架,它将生成任务分解为LLM可管理的分层子模块。HiVeGen通过将自动设计空间探索(DSE)集成到层次感知提示生成中,利用这种分层结构的优势,引入基于权重的检索来增强代码重用,并实现实时人机交互以降低纠错成本,从而显著提高生成设计的质量。

🔬 方法详解

问题定义:论文旨在解决大型语言模型(LLM)在生成复杂硬件(如领域专用加速器DSA)的Verilog代码时,难以生成分层结构、容易产生“幻觉”的问题。现有方法通常直接让LLM生成单一代码块,缺乏对硬件设计内在层次结构的理解,导致生成质量不高。

核心思路:HiVeGen的核心思路是将复杂的Verilog生成任务分解为多个LLM可以独立管理的、具有层次结构的子模块。通过分而治之,降低了每个子模块的生成难度,从而提高了整体代码的质量和可维护性。同时,利用分层结构进行设计空间探索和代码重用。

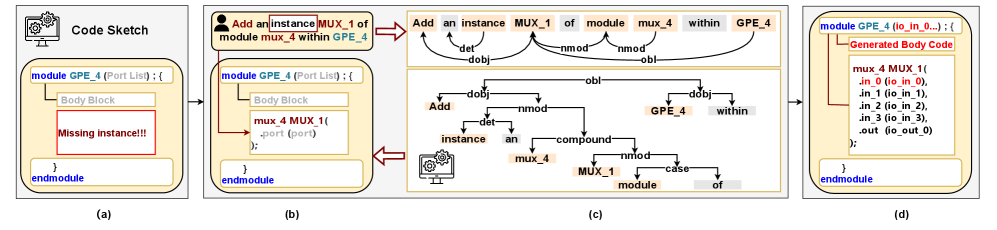

技术框架:HiVeGen框架包含以下几个主要模块:1) 层次分解模块:将顶层设计需求分解为多个子模块,形成层次结构。2) 层次感知提示生成模块:根据子模块在层次结构中的位置和功能,生成定制化的提示,引导LLM生成相应的Verilog代码。3) 基于权重的代码检索模块:从已有的代码库中检索与当前子模块相似的代码片段,作为LLM生成的参考,提高代码质量和重用率。4) 自动设计空间探索模块:在层次结构的不同层级,探索不同的设计参数组合,优化整体性能。5) 人机交互模块:允许用户实时审查和修改LLM生成的代码,降低错误纠正成本。

关键创新:HiVeGen的关键创新在于其层次化的生成方式,以及将自动设计空间探索、代码重用和人机交互集成到LLM驱动的硬件设计流程中。与传统的单一代码块生成方法相比,HiVeGen能够更好地利用硬件设计的内在结构,生成更高质量、更可维护的Verilog代码。

关键设计:HiVeGen中,层次分解策略至关重要,需要根据具体硬件设计的特点进行调整。基于权重的代码检索模块使用语义相似度作为权重,选择最相关的代码片段。自动设计空间探索模块采用遗传算法或强化学习等方法,搜索最优的设计参数组合。人机交互模块提供友好的用户界面,方便用户审查和修改代码。

🖼️ 关键图片

📊 实验亮点

HiVeGen通过分层生成、设计空间探索和代码重用等机制,显著提高了Verilog代码的生成质量。实验结果表明,HiVeGen生成的代码在复杂性、正确性和性能方面均优于直接使用LLM生成的代码。具体提升幅度未知,但论文强调了其在复杂设计上的优势。

🎯 应用场景

HiVeGen可应用于各种领域专用加速器(DSA)和复杂数字电路的设计。通过自动化Verilog代码生成,可以显著缩短芯片设计周期,降低设计成本,并加速新硬件的开发和部署。该框架还可用于教育领域,帮助学生更好地理解和掌握硬件设计方法。

📄 摘要(原文)

With Large Language Models (LLMs) recently demonstrating impressive proficiency in code generation, it is promising to extend their abilities to Hardware Description Language (HDL). However, LLMs tend to generate single HDL code blocks rather than hierarchical structures for hardware designs, leading to hallucinations, particularly in complex designs like Domain-Specific Accelerators (DSAs). To address this, we propose HiVeGen, a hierarchical LLM-based Verilog generation framework that decomposes generation tasks into LLM-manageable hierarchical submodules. HiVeGen further harnesses the advantages of such hierarchical structures by integrating automatic Design Space Exploration (DSE) into hierarchy-aware prompt generation, introducing weight-based retrieval to enhance code reuse, and enabling real-time human-computer interaction to lower error-correction cost, significantly improving the quality of generated designs.