Effective Analog ICs Floorplanning with Relational Graph Neural Networks and Reinforcement Learning

作者: Davide Basso, Luca Bortolussi, Mirjana Videnovic-Misic, Husni Habal

分类: cs.LG, cs.AI, eess.SY

发布日期: 2024-11-20

备注: 7 pages, 7 figures, Accepted at DATE25

💡 一句话要点

提出基于关系图神经网络和强化学习的模拟IC自动布局规划方法

🎯 匹配领域: 支柱二:RL算法与架构 (RL & Architecture)

关键词: 模拟IC布局规划 强化学习 关系图神经网络 自动布局 电路设计

📋 核心要点

- 模拟IC布局规划复杂且耗时,依赖人工经验,难以应对定制化需求和各种约束。

- 利用强化学习自动探索布局方案,并用关系图神经网络编码电路特征和约束,提升泛化能力。

- 实验表明,该方法在速度、面积和线长方面优于传统方法,并显著减少了布局时间。

📝 摘要(中文)

模拟集成电路(IC)布局规划通常是由布局工程师手动完成的,组件(器件和模块)的放置需要精心设计。布局规划和布线步骤的相互依赖性、大量的电气和布局相关约束,以及模拟设计中高度的定制化需求,进一步增加了这一过程的复杂性。本文提出了一种基于强化学习的全新自动布局规划算法。该算法利用关系图卷积神经网络模型来编码电路特征和位置约束。这两种机器学习方法的结合,使得知识能够在具有不同拓扑结构和约束的不同电路设计之间进行迁移,从而提高了解决方案的泛化能力。应用于6个工业电路的实验表明,我们的方法在速度、面积和半周长线长方面均优于已有的布局规划技术。当集成到布局完成的程序生成器中时,与手动布局相比,总体布局时间减少了67.3%,平均面积减少了8.3%。

🔬 方法详解

问题定义:模拟IC布局规划旨在确定电路中各个组件的最佳位置,以满足性能、面积和功耗等方面的要求。传统方法依赖人工经验,耗时且容易出错,难以应对复杂的约束条件和定制化需求。现有自动布局工具在模拟电路上的表现往往不如人工设计,主要痛点在于难以有效建模电路的复杂关系和约束。

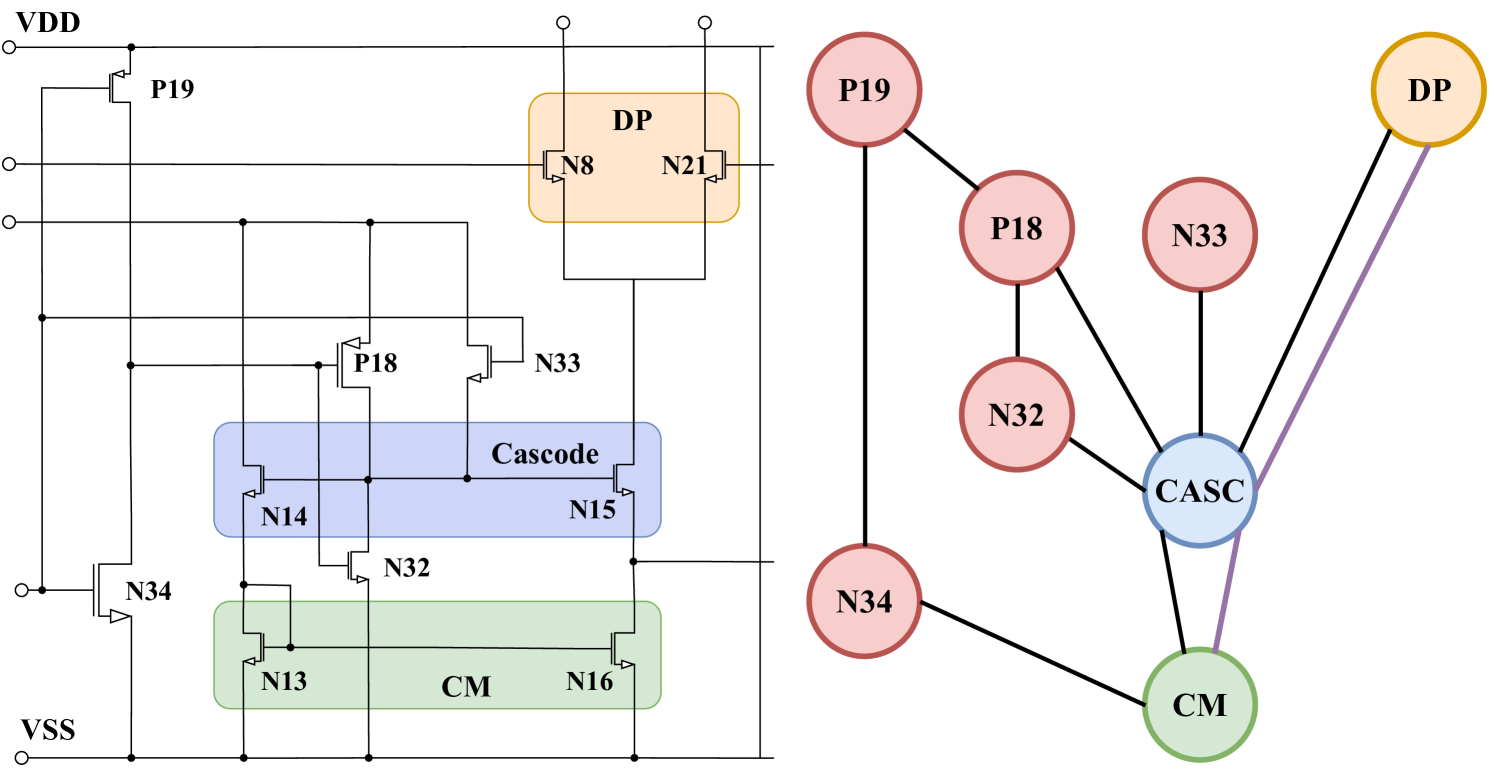

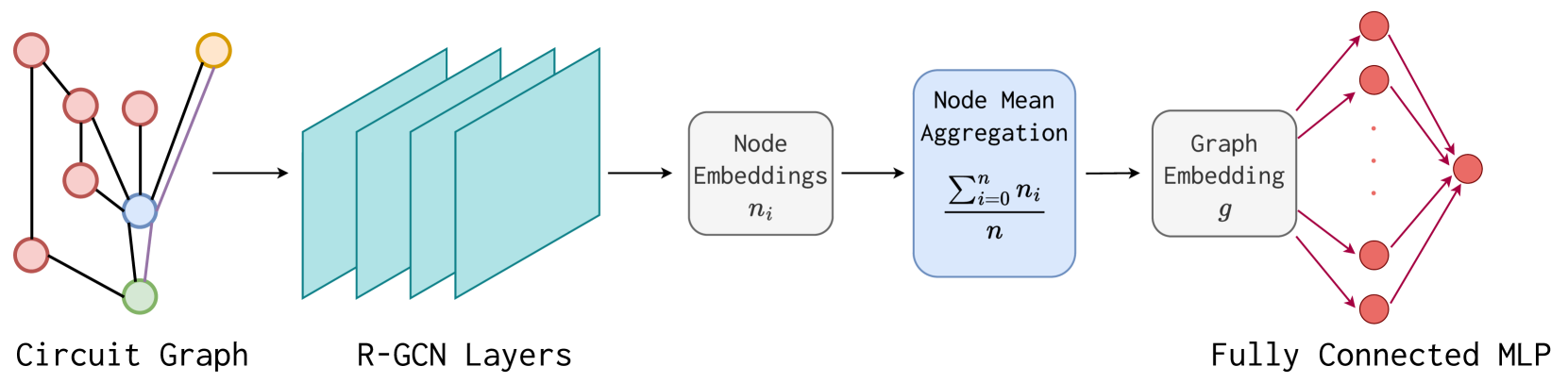

核心思路:本文的核心思路是将布局规划问题建模为强化学习任务,通过智能体与环境的交互,学习最优的布局策略。利用关系图神经网络(RGNN)提取电路的特征和约束信息,为强化学习提供更有效的状态表示,从而提高学习效率和泛化能力。这种结合使得智能体能够理解电路的拓扑结构和约束关系,从而做出更合理的布局决策。

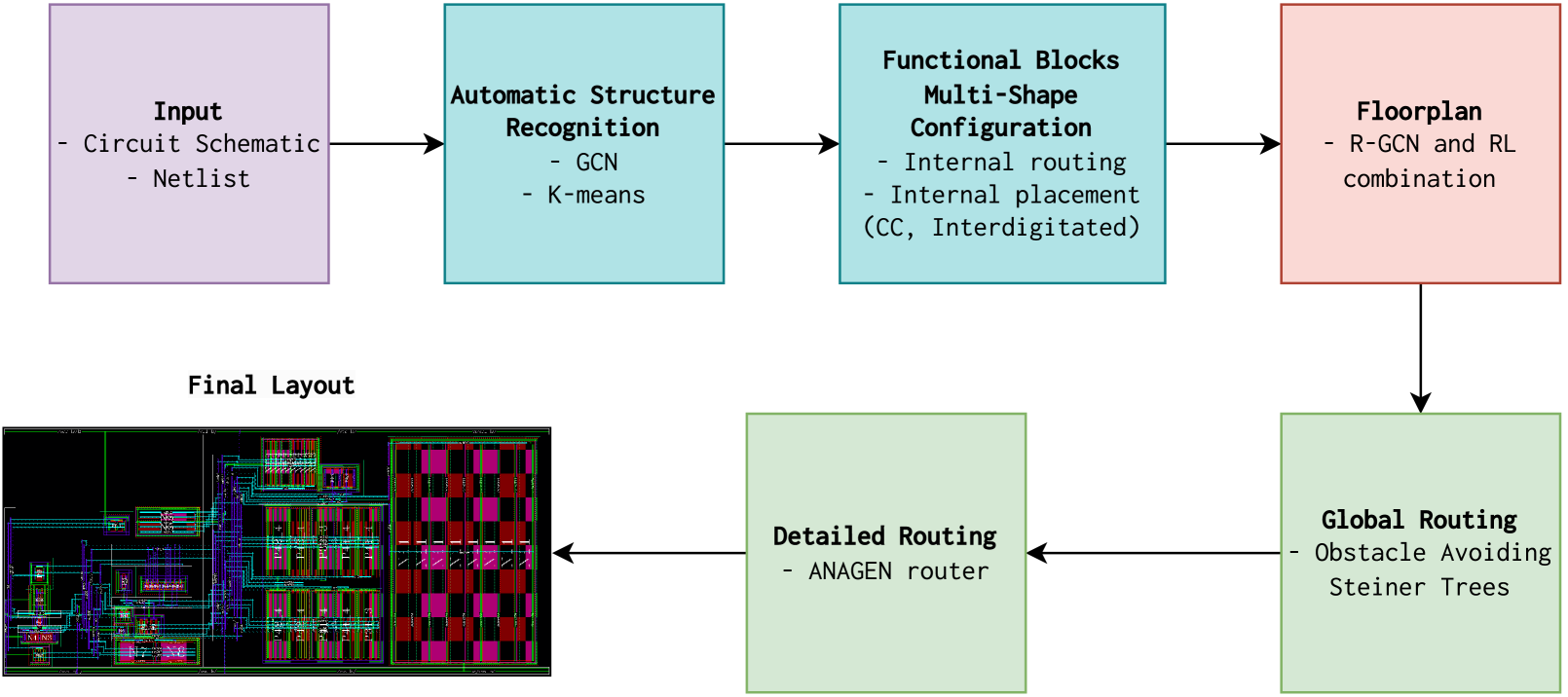

技术框架:该方法的整体框架包含以下几个主要模块:1)电路信息提取模块:从电路网表中提取组件类型、连接关系等信息。2)关系图构建模块:将电路表示为关系图,节点表示组件,边表示组件之间的连接关系和约束。3)RGNN编码模块:利用RGNN对关系图进行编码,提取电路的特征向量。4)强化学习智能体:基于提取的特征向量,智能体选择布局动作,并根据环境的反馈(奖励)更新策略。5)布局评估模块:评估当前布局的性能指标,如面积、线长等,作为强化学习的奖励信号。

关键创新:该方法最重要的技术创新点在于将关系图神经网络引入到模拟IC布局规划中。RGNN能够有效地建模电路的复杂关系和约束,为强化学习提供更丰富的状态信息。与传统的基于启发式算法或模拟退火的布局方法相比,该方法能够学习到更优的布局策略,并具有更好的泛化能力。此外,将强化学习与程序生成器集成,实现了端到端的自动布局流程。

关键设计:RGNN的网络结构包括多个图卷积层,用于聚合邻居节点的信息。损失函数的设计需要考虑多个目标,如最小化面积、线长等。强化学习算法采用Actor-Critic框架,Actor网络负责选择布局动作,Critic网络负责评估当前状态的价值。奖励函数的设计至关重要,需要平衡不同性能指标之间的关系。具体参数设置(如学习率、折扣因子等)需要根据实际电路进行调整。

🖼️ 关键图片

📊 实验亮点

在6个工业电路上的实验结果表明,该方法在速度、面积和半周长线长方面均优于已有的布局规划技术。与手动布局相比,集成到程序生成器后,总体布局时间减少了67.3%,平均面积减少了8.3%。这些结果表明该方法具有很强的实用价值和竞争力。

🎯 应用场景

该研究成果可应用于模拟集成电路的自动布局规划,加速芯片设计流程,降低设计成本,并提高芯片性能。尤其适用于定制化程度高、约束条件复杂的模拟电路设计。未来可进一步扩展到混合信号电路和三维集成电路的布局规划,具有广阔的应用前景。

📄 摘要(原文)

Analog integrated circuit (IC) floorplanning is typically a manual process with the placement of components (devices and modules) planned by a layout engineer. This process is further complicated by the interdependence of floorplanning and routing steps, numerous electric and layout-dependent constraints, as well as the high level of customization expected in analog design. This paper presents a novel automatic floorplanning algorithm based on reinforcement learning. It is augmented by a relational graph convolutional neural network model for encoding circuit features and positional constraints. The combination of these two machine learning methods enables knowledge transfer across different circuit designs with distinct topologies and constraints, increasing the \emph{generalization ability} of the solution. Applied to $6$ industrial circuits, our approach surpassed established floorplanning techniques in terms of speed, area and half-perimeter wire length. When integrated into a \emph{procedural generator} for layout completion, overall layout time was reduced by $67.3\%$ with a $8.3\%$ mean area reduction compared to manual layout.