Automated and Holistic Co-design of Neural Networks and ASICs for Enabling In-Pixel Intelligence

作者: Shubha R. Kharel, Prashansa Mukim, Piotr Maj, Grzegorz W. Deptuch, Shinjae Yoo, Yihui Ren, Soumyajit Mandal

分类: cs.LG, cs.AI, cs.AR

发布日期: 2024-07-18

备注: 18 pages, 17 figures

💡 一句话要点

提出基于贝叶斯优化的神经网络与ASIC协同设计方法,实现像素内智能

🎯 匹配领域: 支柱八:物理动画 (Physics-based Animation)

关键词: 神经网络 ASIC 协同设计 贝叶斯优化 边缘计算

📋 核心要点

- 现有方法在神经网络架构搜索中对硬件的理论理解过于理想化,无法为实际实现提供充分指导。

- 本文提出一种基于多目标贝叶斯优化的智能搜索方法,将神经网络搜索和ASIC综合集成,实现协同设计。

- 实验结果表明,该方法能够找到有效的神经网络Pareto最优设计,用于从读出ASIC像素内的输入脉冲中实时提取特征。

📝 摘要(中文)

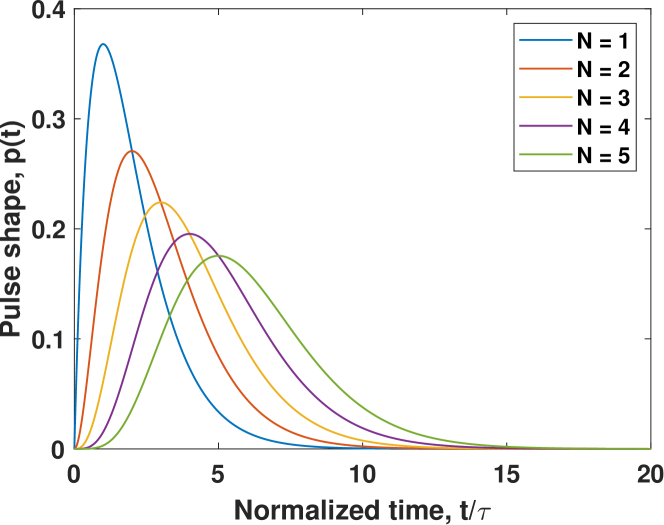

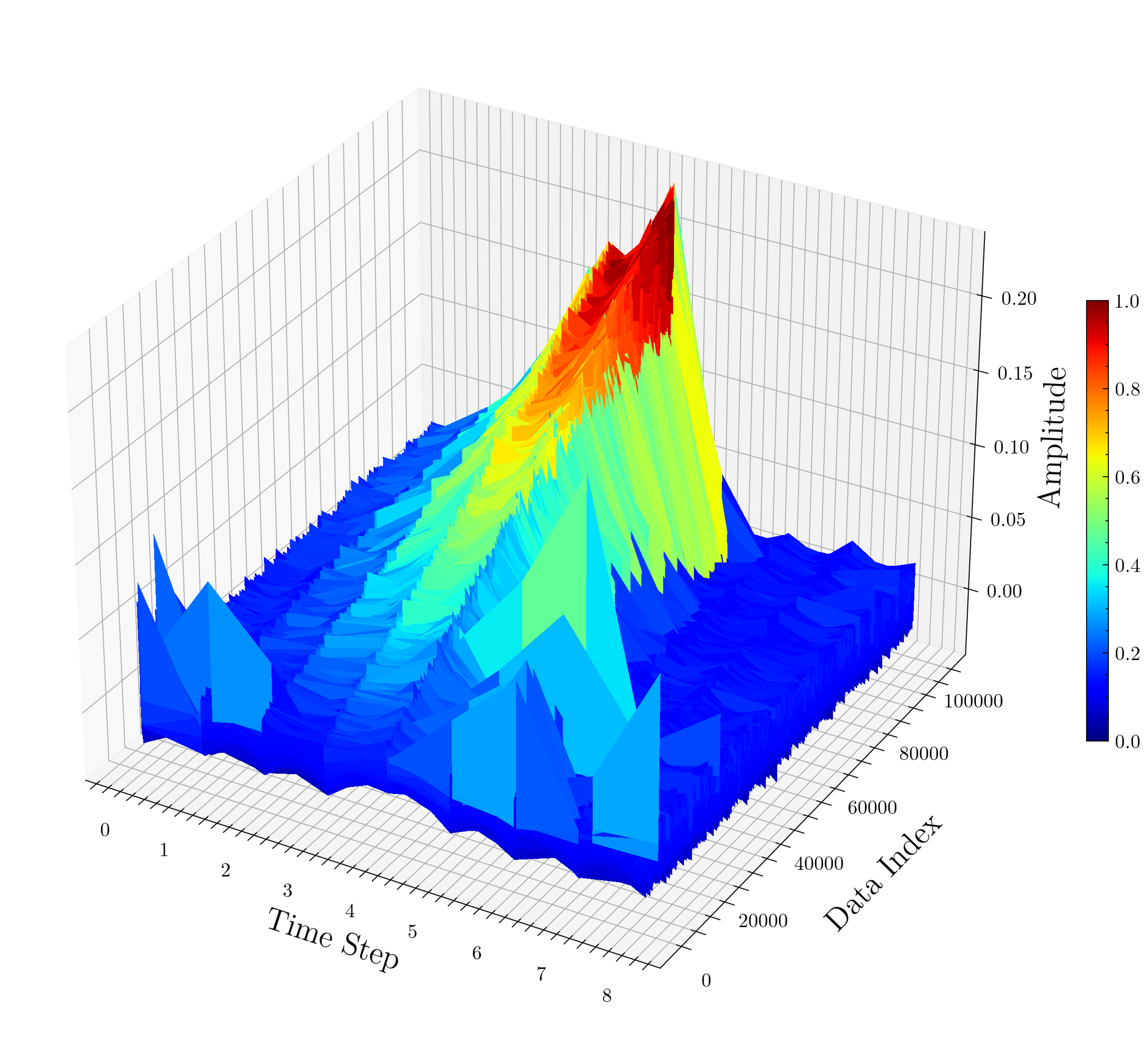

针对极端边缘AI系统(如辐射探测读出ASIC)在微米级尺寸、亚毫瓦功耗和纳秒级速度等严格硬件约束下,需要提供优于传统架构的精度优势的问题,本文提出了一种自动且整体的神经网络和ASIC协同设计方法。该方法利用多目标贝叶斯优化进行智能搜索,将神经网络搜索和ASIC综合集成在一个循环中,从而提供关于所有跨域设计选择的集体影响的可靠反馈。通过寻找用于从读出ASIC的单个像素内的输入脉冲中实时提取特征的有效神经网络的Pareto最优设计选择,展示了该方法的有效性。

🔬 方法详解

问题定义:论文旨在解决极端边缘AI系统中,神经网络和ASIC协同设计面临的挑战。现有方法依赖于对硬件的理论理解进行架构搜索,但理论假设过于理想化,无法指导实际实现。此外,许多关键指标(如延迟)的理论估计不存在,且受工艺设计套件(PDK)参数影响,导致设计空间巨大且难以手动搜索最优解。

核心思路:论文的核心思路是采用智能搜索方法,即多目标贝叶斯优化,将神经网络架构搜索和ASIC综合集成在一个优化循环中。通过这种方式,可以获得关于跨域设计选择的集体影响的可靠反馈,从而在满足硬件约束的同时,优化神经网络的性能。

技术框架:整体框架包含神经网络架构搜索和ASIC综合两个主要模块。神经网络架构搜索模块负责生成不同的神经网络架构,ASIC综合模块负责将这些架构映射到具体的硬件实现。多目标贝叶斯优化器根据ASIC综合的结果(如功耗、延迟、面积)和神经网络的性能指标(如精度)进行评估,并指导下一轮的神经网络架构搜索,形成一个闭环优化过程。

关键创新:该方法最重要的创新点在于将神经网络架构搜索和ASIC综合集成在一个优化循环中,实现了自动且整体的协同设计。与现有方法相比,该方法能够更准确地评估设计选择的实际影响,并找到满足硬件约束的最优解。

关键设计:论文中,多目标贝叶斯优化器用于搜索Pareto最优解,即在满足所有约束条件(如功耗、延迟、面积)的前提下,尽可能提高神经网络的性能。具体的神经网络架构和ASIC实现细节(如网络层数、连接方式、晶体管尺寸等)由优化器自动搜索确定。

🖼️ 关键图片

📊 实验亮点

论文通过实验验证了该方法的有效性,能够找到用于从读出ASIC的单个像素内的输入脉冲中实时提取特征的有效神经网络的Pareto最优设计选择。具体性能数据和对比基线在论文中给出,展示了该方法在精度、功耗和延迟等方面的优势。

🎯 应用场景

该研究成果可应用于各种极端边缘AI系统,例如辐射探测、环境监测、可穿戴设备等。通过自动协同设计神经网络和ASIC,可以显著提高这些系统的性能和效率,并降低开发成本。未来,该方法有望推广到更广泛的硬件加速器设计领域。

📄 摘要(原文)

Extreme edge-AI systems, such as those in readout ASICs for radiation detection, must operate under stringent hardware constraints such as micron-level dimensions, sub-milliwatt power, and nanosecond-scale speed while providing clear accuracy advantages over traditional architectures. Finding ideal solutions means identifying optimal AI and ASIC design choices from a design space that has explosively expanded during the merger of these domains, creating non-trivial couplings which together act upon a small set of solutions as constraints tighten. It is impractical, if not impossible, to manually determine ideal choices among possibilities that easily exceed billions even in small-size problems. Existing methods to bridge this gap have leveraged theoretical understanding of hardware to f architecture search. However, the assumptions made in computing such theoretical metrics are too idealized to provide sufficient guidance during the difficult search for a practical implementation. Meanwhile, theoretical estimates for many other crucial metrics (like delay) do not even exist and are similarly variable, dependent on parameters of the process design kit (PDK). To address these challenges, we present a study that employs intelligent search using multi-objective Bayesian optimization, integrating both neural network search and ASIC synthesis in the loop. This approach provides reliable feedback on the collective impact of all cross-domain design choices. We showcase the effectiveness of our approach by finding several Pareto-optimal design choices for effective and efficient neural networks that perform real-time feature extraction from input pulses within the individual pixels of a readout ASIC.