CIRCUITSYNTH: Leveraging Large Language Models for Circuit Topology Synthesis

作者: Prashanth Vijayaraghavan, Luyao Shi, Ehsan Degan, Xin Zhang

分类: cs.LG, cs.AI, cs.ET

发布日期: 2024-06-06

备注: 6 pages, 1 figure, LAD'24

💡 一句话要点

提出CIRCUITSYNTH,利用大语言模型自动合成电路拓扑

🎯 匹配领域: 支柱九:具身大模型 (Embodied Foundation Models)

关键词: 电路拓扑生成 大型语言模型 自动化设计 电子电路 电路优化

📋 核心要点

- 电路拓扑生成是电路设计的核心,但传统方法耗时且易出错,面临自动化挑战。

- CIRCUITSYNTH利用LLM学习电路拓扑的有效模式,通过生成和优化两个阶段自动合成电路。

- 实验表明,CIRCUITSYNTH优于微调的LLM变体,为提升电路性能和满足设计需求奠定基础。

📝 摘要(中文)

本文介绍了一种名为CIRCUITSYNTH的新方法,该方法利用大型语言模型(LLM)来促进有效电路拓扑的自动合成。电路拓扑生成在电子电路设计中起着关键作用,它影响着电路的基本功能。CIRCUITSYNTH采用了一种复杂的两阶段方法,包括电路拓扑生成和电路拓扑优化,并使用包含有效和无效电路配置的数据集进行训练。实验结果表明,与各种微调的LLM变体相比,CIRCUITSYNTH具有有效性。该方法为未来旨在提高电路效率和指定输出电压的研究奠定了基础,从而能够自动生成具有改进的性能并符合设计要求的电路拓扑。

🔬 方法详解

问题定义:电路拓扑生成旨在根据给定的功能需求自动设计电路结构。现有方法通常依赖于人工经验或基于规则的算法,效率低下且难以处理复杂电路。痛点在于缺乏一种能够自动、高效且准确地生成有效电路拓扑的通用方法。

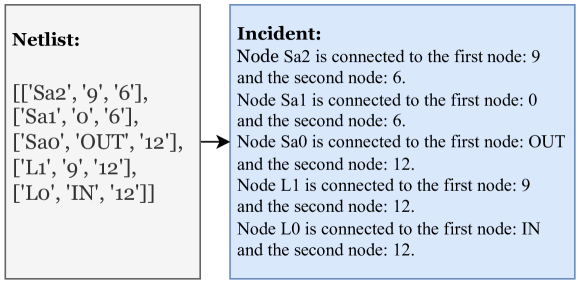

核心思路:CIRCUITSYNTH的核心思路是利用大型语言模型(LLM)强大的学习和生成能力,将电路拓扑生成问题转化为序列生成问题。通过训练LLM学习大量电路拓扑数据,使其能够理解电路元件之间的连接关系和电路设计的规则,从而自动生成新的、有效的电路拓扑结构。

技术框架:CIRCUITSYNTH采用两阶段方法:电路拓扑生成和电路拓扑优化。在电路拓扑生成阶段,LLM基于输入提示(例如,所需的功能或性能指标)生成初始的电路拓扑结构。在电路拓扑优化阶段,LLM对生成的拓扑结构进行迭代改进,以提高电路性能并满足设计约束。整个流程可以看作是一个LLM驱动的电路设计循环。

关键创新:CIRCUITSYNTH的关键创新在于将LLM应用于电路拓扑生成领域。与传统的基于规则或优化的方法不同,CIRCUITSYNTH能够从数据中学习复杂的电路设计模式,并生成具有创造性的电路拓扑结构。此外,两阶段方法允许对生成的拓扑结构进行迭代改进,从而提高电路性能。

关键设计:CIRCUITSYNTH的关键设计包括:1)构建包含有效和无效电路配置的大规模数据集,用于训练LLM;2)设计合适的输入提示,以指导LLM生成满足特定需求的电路拓扑;3)开发有效的优化策略,以提高电路性能并满足设计约束。具体的参数设置、损失函数和网络结构等技术细节在论文中可能未详细描述,属于未知信息。

🖼️ 关键图片

📊 实验亮点

CIRCUITSYNTH的实验结果表明,其性能优于各种微调的LLM变体。具体的性能数据和提升幅度在摘要中未明确给出,属于未知信息。但结论表明,该方法在电路拓扑生成方面具有显著优势,为后续研究奠定了基础。

🎯 应用场景

CIRCUITSYNTH具有广泛的应用前景,可用于自动化电路设计、定制化电路生成、以及电路优化等领域。它可以显著缩短电路设计周期,降低设计成本,并提高电路性能。未来,CIRCUITSYNTH有望成为电路设计工程师的重要辅助工具,推动电子电路设计的智能化和自动化。

📄 摘要(原文)

Circuit topology generation plays a crucial role in the design of electronic circuits, influencing the fundamental functionality of the circuit. In this paper, we introduce CIRCUITSYNTH, a novel approach that harnesses LLMs to facilitate the automated synthesis of valid circuit topologies. With a dataset comprising both valid and invalid circuit configurations, CIRCUITSYNTH employs a sophisticated two-phase methodology, comprising Circuit Topology Generation and Circuit Topology Refinement. Experimental results demonstrate the effectiveness of CIRCUITSYNTH compared to various fine-tuned LLM variants. Our approach lays the foundation for future research aimed at enhancing circuit efficiency and specifying output voltage, thus enabling the automated generation of circuit topologies with improved performance and adherence to design requirements.