TLC-Plan: A Two-Level Codebook Based Network for End-to-End Vector Floorplan Generation

作者: Biao Xiong, Zhen Peng, Ping Wang, Qiegen Liu, Xian Zhong

分类: cs.CV

发布日期: 2026-02-06

🔗 代码/项目: GITHUB

💡 一句话要点

TLC-Plan:一种基于双层码本网络的端到端矢量户型图生成方法

🎯 匹配领域: 支柱四:生成式动作 (Generative Motion)

关键词: 矢量户型图生成 双层VQ-VAE 自回归Transformer 端到端学习 建筑设计

📋 核心要点

- 现有户型图生成方法依赖栅格空间和后处理矢量化,导致结构不一致,限制了端到端学习。

- TLC-Plan提出一种分层生成模型,利用双层VQ-VAE编码全局布局和局部几何,直接生成矢量户型图。

- 实验表明,TLC-Plan在RPLAN和LIFULL数据集上取得了优异性能,实现了约束感知和可扩展的矢量户型图生成。

📝 摘要(中文)

本文提出了一种名为TLC-Plan的层级生成模型,用于直接从输入边界合成矢量户型图,旨在提高设计质量、建筑效率和可持续性。现有方法通常在栅格空间中操作,并依赖于事后矢量化,这引入了结构不一致性并阻碍了端到端学习。TLC-Plan采用双层VQ-VAE将全局布局编码为语义标记的房间边界框,并使用多边形级代码细化局部几何形状。这种层次结构在CodeTree表示中统一,而自回归Transformer对以边界为条件的code进行采样,以生成多样且拓扑有效的方案,无需显式的房间拓扑或尺寸先验。在RPLAN数据集(FID = 1.84,MSE = 2.06)上取得了最先进的性能,并在LIFULL数据集上取得了领先的结果。该框架推进了面向实际建筑应用的、具有约束感知和可扩展性的矢量户型图生成。

🔬 方法详解

问题定义:现有户型图生成方法主要在栅格图像上进行,然后通过矢量化算法转换为矢量图。这种方式容易引入结构不一致性,例如房间之间的连接不准确,墙体厚度不统一等,并且无法进行端到端的优化,限制了生成质量。此外,现有方法通常需要预先定义房间的拓扑结构或尺寸先验,限制了生成的多样性和灵活性。

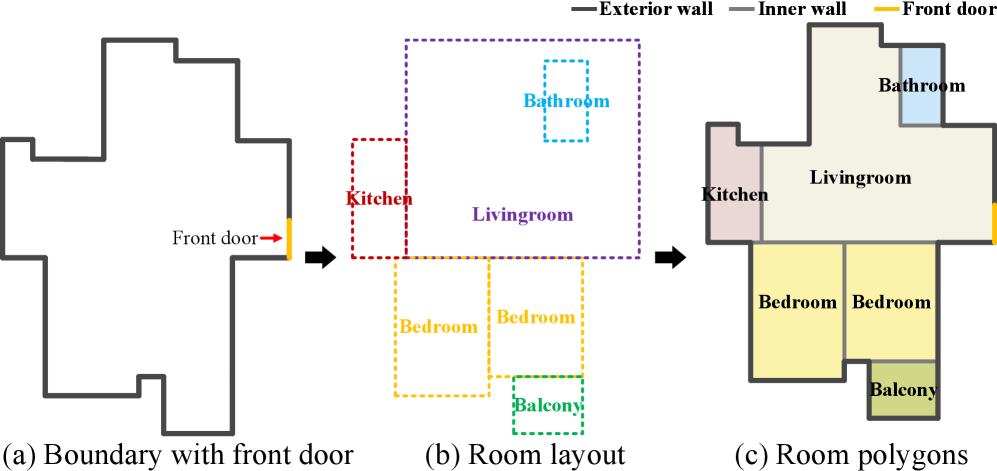

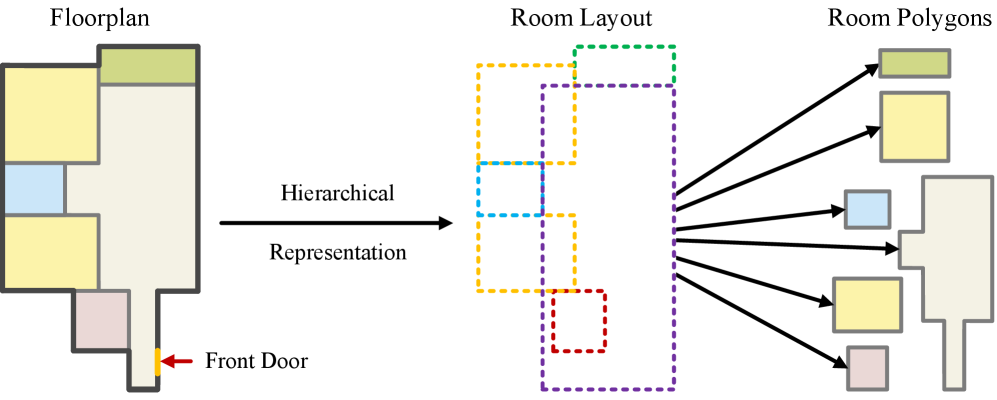

核心思路:TLC-Plan的核心思路是模拟人类建筑师的设计流程,即先确定房间的布局,再细化房间的几何形状。通过分层编码的方式,将全局布局和局部几何信息分别表示,并使用自回归模型进行生成。这种分层结构能够更好地捕捉户型图的结构信息,并生成拓扑有效的矢量户型图。

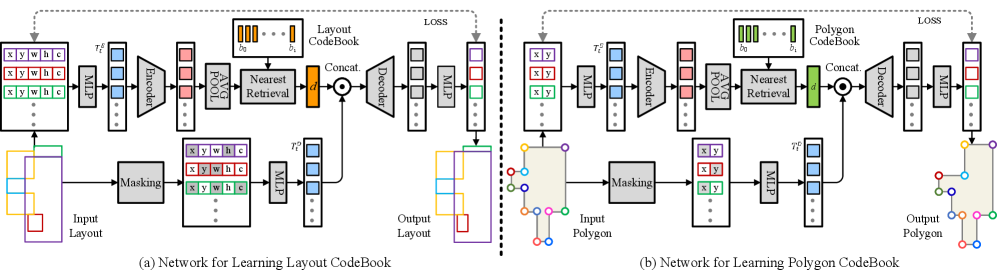

技术框架:TLC-Plan的整体框架包含以下几个主要模块:1) 双层VQ-VAE:用于编码全局布局(房间边界框)和局部几何(多边形级代码)。第一层VQ-VAE编码房间的布局信息,第二层VQ-VAE编码房间的几何形状信息。2) CodeTree表示:将两层VQ-VAE的编码结果组织成树状结构,方便自回归模型的学习。3) 自回归Transformer:用于生成CodeTree,从而生成矢量户型图。Transformer以户型图的边界作为条件,逐步生成CodeTree中的节点。

关键创新:TLC-Plan的关键创新在于:1) 提出了一种双层VQ-VAE结构,能够有效地编码全局布局和局部几何信息。2) 提出了一种CodeTree表示,能够将分层编码的结果组织成树状结构,方便自回归模型的学习。3) 实现了端到端的矢量户型图生成,无需后处理矢量化。

关键设计:TLC-Plan的关键设计包括:1) 使用VQ-VAE进行离散化编码,能够有效地减少模型的学习难度。2) 使用Transformer作为自回归模型,能够捕捉长距离依赖关系。3) 使用交叉熵损失函数训练VQ-VAE和Transformer。4) 在训练过程中,使用数据增强技术,例如旋转、缩放和平移,以提高模型的泛化能力。

🖼️ 关键图片

📊 实验亮点

TLC-Plan在RPLAN数据集上取得了最先进的性能,FID得分为1.84,MSE为2.06。同时,在LIFULL数据集上也取得了领先的结果。相较于现有方法,TLC-Plan能够生成更高质量、更符合实际需求的矢量户型图,并且具有更好的可扩展性和灵活性。

🎯 应用场景

TLC-Plan在建筑设计、室内设计、房地产等领域具有广泛的应用前景。它可以用于快速生成各种户型图,辅助建筑师进行方案设计,提高设计效率。此外,TLC-Plan还可以用于生成虚拟现实场景,为用户提供沉浸式的房屋体验。未来,该技术有望应用于智能家居、城市规划等领域,实现更智能、更高效的建筑设计和管理。

📄 摘要(原文)

Automated floorplan generation aims to improve design quality, architectural efficiency, and sustainability by jointly modeling global spatial organization and precise geometric detail. However, existing approaches operate in raster space and rely on post hoc vectorization, which introduces structural inconsistencies and hinders end-to-end learning. Motivated by compositional spatial reasoning, we propose TLC-Plan, a hierarchical generative model that directly synthesizes vector floorplans from input boundaries, aligning with human architectural workflows based on modular and reusable patterns. TLC-Plan employs a two-level VQ-VAE to encode global layouts as semantically labeled room bounding boxes and to refine local geometries using polygon-level codes. This hierarchy is unified in a CodeTree representation, while an autoregressive transformer samples codes conditioned on the boundary to generate diverse and topologically valid designs, without requiring explicit room topology or dimensional priors. Extensive experiments show state-of-the-art performance on RPLAN dataset (FID = 1.84, MSE = 2.06) and leading results on LIFULL dataset. The proposed framework advances constraint-aware and scalable vector floorplan generation for real-world architectural applications. Source code and trained models are released at https://github.com/rosolose/TLC-PLAN.