Accelerating Post-Quantum Cryptography via LLM-Driven Hardware-Software Co-Design

作者: Yuchao Liao, Tosiron Adegbija, Roman Lysecky

分类: cs.AR, cs.AI

发布日期: 2026-02-10

备注: Accepted at the 27th International Symposium on Quality Electronic Design (ISQED 2026)

💡 一句话要点

利用LLM驱动的软硬件协同设计加速后量子密码学

🎯 匹配领域: 支柱九:具身大模型 (Embodied Foundation Models)

关键词: 后量子密码学 大型语言模型 硬件加速 软硬件协同设计 FPGA FALCON 自动化设计 代码生成

📋 核心要点

- 后量子密码算法计算复杂度高,硬件实现效率低,成为安全领域的挑战。

- 利用LLM分析PQC算法,识别性能瓶颈,并自动生成FPGA硬件描述,实现软硬件协同设计。

- 实验表明,LLM驱动的加速器设计相比传统HLS方法,在内核执行速度上提升高达2.6倍。

📝 摘要(中文)

后量子密码学(PQC)对于保护数据免受新兴量子威胁至关重要。然而,其算法计算复杂,难以在硬件上高效实现。本文探讨了大型语言模型(LLM)在加速PQC软硬件协同设计过程中的潜力,重点关注FALCON数字签名方案。我们提出了一个新颖的框架,该框架利用LLM分析PQC算法,识别性能关键组件,并生成用于FPGA实现的候选硬件描述。我们首次对FALCON中低级计算密集型内核的LLM驱动综合与传统HLS方法进行了定量比较,结果表明,人工参与的LLM生成的加速器在内核执行时间上可实现高达2.6倍的加速,并具有更短的关键路径,同时也突出了资源利用率和功耗方面的权衡。我们的结果表明,LLM可以通过自动化PQC算法的FPGA加速器设计迭代来最大限度地减少设计工作量和开发时间,为FPGA上快速和自适应的PQC加速器设计提供了一个有希望的新方向。

🔬 方法详解

问题定义:后量子密码学(PQC)算法的计算复杂度高,直接在硬件上高效实现非常困难。传统的手工设计或基于高级综合(HLS)的方法,在设计空间探索和优化方面效率较低,难以充分挖掘硬件加速的潜力。因此,如何快速有效地设计PQC算法的硬件加速器是一个亟待解决的问题。

核心思路:利用大型语言模型(LLM)的强大代码生成和理解能力,自动化硬件加速器的设计过程。LLM可以分析PQC算法的结构,识别计算密集型的关键内核,并根据性能指标生成优化的硬件描述代码。通过人机协作,可以快速迭代设计方案,探索更优的硬件架构。

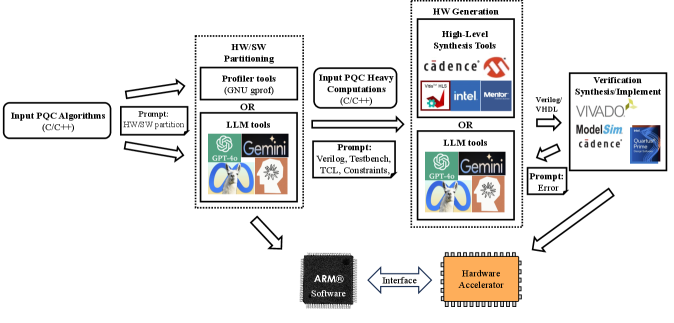

技术框架:该框架包含以下几个主要阶段:1) PQC算法分析:使用LLM分析PQC算法的源代码,提取关键的计算内核。2) 硬件描述生成:根据性能需求和硬件约束,LLM生成候选的硬件描述代码(例如,VHDL或Verilog)。3) 硬件综合与评估:将生成的硬件描述代码进行综合,并在FPGA上进行实现和评估。4) 人工干预与优化:根据评估结果,人工对LLM生成的代码进行调整和优化,并反馈给LLM进行迭代学习。

关键创新:该方法的核心创新在于利用LLM自动化硬件加速器的设计过程,减少了人工干预,加速了设计迭代。与传统的HLS方法相比,LLM可以更好地理解算法的语义,生成更优化的硬件描述代码。此外,人机协作的模式可以充分发挥LLM的自动化能力和人类的专业知识。

关键设计:该论文重点关注FALCON数字签名方案的加速器设计。LLM被用于生成FALCON算法中关键内核的硬件描述代码,例如多项式乘法和快速傅里叶变换(FFT)等。在实验中,研究人员探索了不同的LLM提示策略和硬件约束条件,以优化加速器的性能、资源利用率和功耗。

🖼️ 关键图片

📊 实验亮点

实验结果表明,对于FALCON数字签名方案中的关键内核,LLM驱动的硬件加速器设计相比传统的HLS方法,在内核执行时间上实现了高达2.6倍的加速。同时,LLM生成的加速器具有更短的关键路径。虽然在资源利用率和功耗方面存在一定的权衡,但总体而言,LLM驱动的设计方法能够显著提升PQC算法的硬件加速效率。

🎯 应用场景

该研究成果可应用于各种需要后量子密码保护的场景,例如安全通信、数据存储、物联网设备等。通过自动化硬件加速器设计,可以降低PQC算法的部署成本,加速其在实际系统中的应用。未来,该方法有望推广到其他密码算法和计算密集型应用领域,实现更高效的硬件加速。

📄 摘要(原文)

Post-quantum cryptography (PQC) is crucial for securing data against emerging quantum threats. However, its algorithms are computationally complex and difficult to implement efficiently on hardware. In this paper, we explore the potential of Large Language Models (LLMs) to accelerate the hardware-software co-design process for PQC, with a focus on the FALCON digital signature scheme. We present a novel framework that leverages LLMs to analyze PQC algorithms, identify performance-critical components, and generate candidate hardware descriptions for FPGA implementation. We present the first quantitative comparison between LLM-driven synthesis and conventional HLS-based approaches for low-level compute-intensive kernels in FALCON, showing that human-in-the-loop LLM-generated accelerators can achieve up to 2.6x speedup in kernel execution time with shorter critical paths, while highlighting trade-offs in resource utilization and power consumption. Our results suggest that LLMs can minimize design effort and development time by automating FPGA accelerator design iterations for PQC algorithms, offering a promising new direction for rapid and adaptive PQC accelerator design on FPGAs.