EvolVE: Evolutionary Search for LLM-based Verilog Generation and Optimization

作者: Wei-Po Hsin, Ren-Hao Deng, Yao-Ting Hsieh, En-Ming Huang, Shih-Hao Hung

分类: cs.AI, cs.NE, cs.PL

发布日期: 2026-01-26

备注: 17 pages, 6 figures, 8 tables

🔗 代码/项目: GITHUB

💡 一句话要点

提出EvolVE框架以优化LLM驱动的Verilog生成

🎯 匹配领域: 支柱九:具身大模型 (Embodied Foundation Models)

关键词: Verilog生成 进化策略 蒙特卡洛树搜索 硬件优化 大型语言模型 集成电路设计 自动化设计 性能优化

📋 核心要点

- 现有方法在Verilog设计中面临劳动密集和专业知识要求高的挑战,且LLMs在捕捉硬件逻辑和并发性方面存在局限。

- EvolVE框架通过分析多种进化策略,结合MCTS和IGR,提供了一种新的自动化Verilog生成与优化方法。

- 实验结果显示,EvolVE在多个基准测试中表现优异,尤其在行业规模问题上显著降低了PPA乘积,提升了设计效率。

📝 摘要(中文)

Verilog的设计周期本质上劳动密集且需要广泛的领域专业知识。尽管大型语言模型(LLMs)提供了自动化的有希望路径,但其有限的训练数据和内在的顺序推理无法捕捉硬件系统中严格的形式逻辑和并发性。为克服这些障碍,我们提出了EvolVE,这是第一个分析多种进化策略在芯片设计任务中的框架,发现蒙特卡洛树搜索(MCTS)在最大化功能正确性方面表现优异,而以理念为指导的优化(IGR)在优化方面更为出色。我们进一步利用结构化测试平台生成(STG)来加速进化过程。为了应对复杂优化基准的缺乏,我们引入了IC-RTL,针对来自国家集成电路竞赛的行业规模问题。评估结果表明,EvolVE在VerilogEval v2上达到了98.1%,在RTLLM v2上达到了92%。此外,在行业规模的IC-RTL套件上,我们的框架超越了竞赛参与者撰写的参考实现,在霍夫曼编码中将功耗、性能、面积(PPA)乘积降低了多达66%,在所有问题的几何平均值中降低了17%。

🔬 方法详解

问题定义:本论文旨在解决Verilog设计过程中的劳动密集性和对领域专业知识的高要求,现有方法在捕捉硬件系统的形式逻辑和并发性方面存在不足。

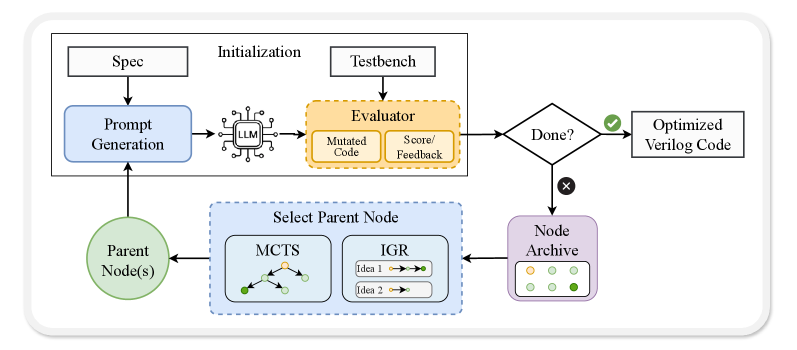

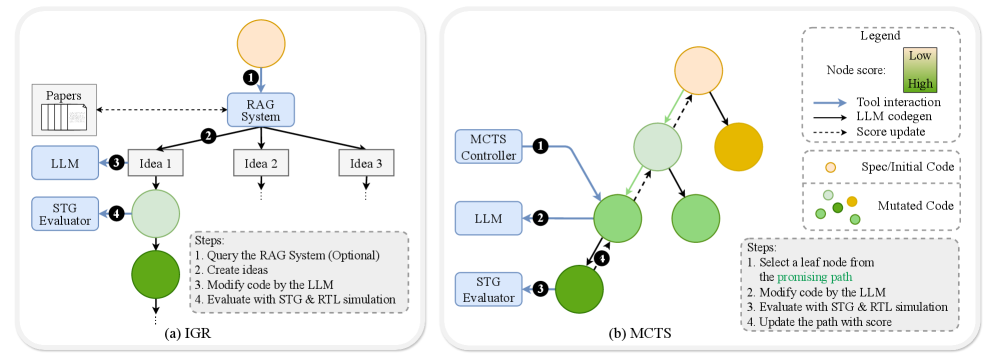

核心思路:EvolVE框架通过分析多种进化策略,特别是蒙特卡洛树搜索(MCTS)和以理念为指导的优化(IGR),实现了对Verilog生成和优化的自动化,旨在提高功能正确性和优化效果。

技术框架:EvolVE的整体架构包括多个模块,首先通过MCTS进行功能正确性的最大化,然后利用IGR进行优化,最后结合结构化测试平台生成(STG)加速进化过程。

关键创新:EvolVE的主要创新在于首次将多种进化策略结合应用于芯片设计任务,特别是MCTS在功能正确性上的优势和IGR在优化上的优越性,使其在行业规模问题上表现出色。

关键设计:在设计中,EvolVE使用了特定的参数设置和损失函数,以确保在进化过程中能够有效评估和优化设计结果,具体细节包括对功能正确性和性能的平衡考虑。

🖼️ 关键图片

📊 实验亮点

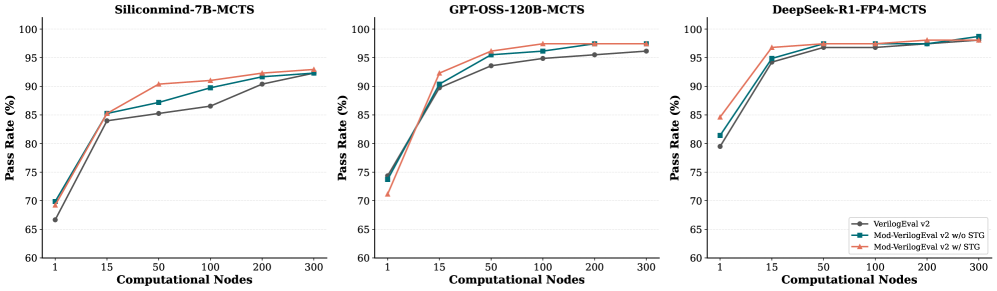

EvolVE在多个基准测试中表现出色,特别是在VerilogEval v2上达到了98.1%的准确率,在RTLLM v2上达到了92%。在行业规模的IC-RTL套件中,EvolVE的PPA乘积在霍夫曼编码中降低了66%,在所有问题的几何平均值中降低了17%,显著优于参考实现。

🎯 应用场景

EvolVE框架的潜在应用领域包括集成电路设计、硬件描述语言生成和优化等。其自动化能力不仅能显著降低设计周期和人力成本,还能提升设计的准确性和效率,具有广泛的实际价值和未来影响。

📄 摘要(原文)

Verilog's design cycle is inherently labor-intensive and necessitates extensive domain expertise. Although Large Language Models (LLMs) offer a promising pathway toward automation, their limited training data and intrinsic sequential reasoning fail to capture the strict formal logic and concurrency inherent in hardware systems. To overcome these barriers, we present EvolVE, the first framework to analyze multiple evolution strategies on chip design tasks, revealing that Monte Carlo Tree Search (MCTS) excels at maximizing functional correctness, while Idea-Guided Refinement (IGR) proves superior for optimization. We further leverage Structured Testbench Generation (STG) to accelerate the evolutionary process. To address the lack of complex optimization benchmarks, we introduce IC-RTL, targeting industry-scale problems derived from the National Integrated Circuit Contest. Evaluations establish EvolVE as the new state-of-the-art, achieving 98.1% on VerilogEval v2 and 92% on RTLLM v2. Furthermore, on the industry-scale IC-RTL suite, our framework surpasses reference implementations authored by contest participants, reducing the Power, Performance, Area (PPA) product by up to 66% in Huffman Coding and 17% in the geometric mean across all problems. The source code of the IC-RTL benchmark is available at https://github.com/weiber2002/ICRTL.