DeepV: A Model-Agnostic Retrieval-Augmented Framework for Verilog Code Generation with a High-Quality Knowledge Base

作者: Zahin Ibnat, Paul E. Calzada, Rasin Mohammed Ihtemam, Sujan Kumar Saha, Jingbo Zhou, Farimah Farahmandi, Mark Tehranipoor

分类: cs.AR, cs.AI

发布日期: 2025-10-06

备注: 22 pages, 6 figures

🔗 代码/项目: HUGGINGFACE

💡 一句话要点

DeepV:一种模型无关的RAG框架,通过高质量知识库提升Verilog代码生成效果。

🎯 匹配领域: 支柱九:具身大模型 (Embodied Foundation Models)

关键词: RTL代码生成 检索增强生成 大型语言模型 硬件设计自动化 Verilog 知识库 模型无关性

📋 核心要点

- 现有基于LLM的RTL代码生成方法难以整合新的IP,导致生成代码质量差,且微调旧模型无法跟上通用LLM的进步。

- DeepV提出一种模型无关的RAG框架,通过检索高质量代码库增强LLM的上下文信息,无需RTL特定训练即可提升代码生成效果。

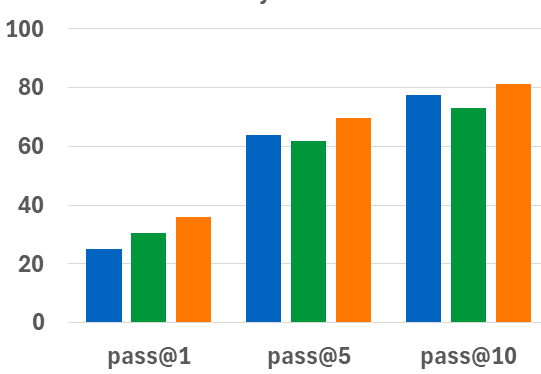

- 实验表明,DeepV框架能够显著提升最新商业LLM(如GPT-5)在VerilogEval基准测试上的性能,提升幅度接近17%。

📝 摘要(中文)

随着大型语言模型(LLMs)不断融入现代技术,代码生成应用的需求日益增长,这自然也扩展到了硬件设计自动化领域。基于LLM的寄存器传输级(RTL)代码生成解决方案,特别是通过微调LLM、提示工程和Agentic方法,在文献中变得流行。然而,这些技术存在一个缺陷,即它们无法将新的IP集成到模型的知识库中,导致生成的代码质量较差。此外,随着通用LLM的不断改进,在旧模型上进行微调的方法将无法在生成更准确和高效的设计方面与之竞争。虽然存在一些检索增强生成(RAG)技术来缓解微调方法中的挑战,但这些工作倾向于利用低质量的代码库,在框架中加入计算成本高昂的微调,或者没有直接在RTL生成步骤中使用RAG。本文介绍DeepV:一个模型无关的RAG框架,通过大型、高质量的数据集增强上下文来生成RTL设计,而无需任何RTL特定的训练。我们的框架使最新的商业LLM,OpenAI的GPT-5,在VerilogEval基准测试中性能提升近17%。我们已将DeepV托管在Hugging Face (HF) Space上,供社区使用。

🔬 方法详解

问题定义:现有基于LLM的RTL代码生成方法,如微调和提示工程,无法有效整合新的IP到模型的知识库中,导致生成代码质量不高。此外,对旧模型进行微调难以跟上通用LLM的发展,无法生成更准确和高效的设计。现有的RAG方法也存在问题,例如使用低质量代码库或包含计算成本高的微调步骤。

核心思路:DeepV的核心思路是利用检索增强生成(RAG)框架,通过检索高质量的Verilog代码片段来增强LLM的上下文信息,从而提高RTL代码生成的质量和效率。这种方法避免了对LLM进行RTL特定的训练或微调,使其能够利用最新的通用LLM的强大能力。

技术框架:DeepV框架主要包含以下几个模块:1) 高质量Verilog代码库:收集并整理大量的Verilog代码,构建高质量的知识库。2) 检索模块:根据输入的自然语言描述,从知识库中检索相关的代码片段。3) 上下文增强模块:将检索到的代码片段与原始输入进行组合,形成增强的上下文信息。4) 代码生成模块:利用LLM(如GPT-5)根据增强的上下文信息生成RTL代码。整个流程无需对LLM进行任何RTL相关的训练。

关键创新:DeepV的关键创新在于其模型无关性以及对高质量知识库的利用。它不依赖于特定的LLM,可以与最新的通用LLM结合使用,从而充分利用LLM的强大能力。此外,DeepV通过构建和维护高质量的Verilog代码库,确保检索到的代码片段具有较高的质量,从而提高生成的RTL代码的准确性和效率。

关键设计:DeepV的关键设计包括:1) 代码库的构建:需要精心选择和整理Verilog代码,确保代码的质量和多样性。2) 检索算法的选择:需要选择合适的检索算法,以便能够快速准确地检索到相关的代码片段。3) 上下文增强策略:需要设计有效的上下文增强策略,将检索到的代码片段与原始输入进行组合,形成有意义的上下文信息。4) 提示工程:设计合适的提示语,引导LLM生成高质量的RTL代码。具体参数设置和网络结构等细节未在论文中详细描述,属于未知信息。

🖼️ 关键图片

📊 实验亮点

DeepV框架在VerilogEval基准测试中取得了显著的性能提升。通过与OpenAI的GPT-5结合使用,DeepV能够使GPT-5的性能提升近17%。这一结果表明,DeepV框架能够有效地利用高质量的知识库来增强LLM的上下文信息,从而提高RTL代码生成的质量。

🎯 应用场景

DeepV框架可应用于硬件设计自动化领域,帮助工程师快速生成高质量的RTL代码,加速IP设计和验证过程。该框架能够降低硬件设计的门槛,提高设计效率,并促进新型硬件架构的探索。未来,DeepV有望集成到更复杂的硬件设计流程中,实现更高级别的自动化。

📄 摘要(原文)

As large language models (LLMs) continue to be integrated into modern technology, there has been an increased push towards code generation applications, which also naturally extends to hardware design automation. LLM-based solutions for register transfer level (RTL) code generation for intellectual property (IP) designs have grown, especially with fine-tuned LLMs, prompt engineering, and agentic approaches becoming popular in literature. However, a gap has been exposed in these techniques, as they fail to integrate novel IPs into the model's knowledge base, subsequently resulting in poorly generated code. Additionally, as general-purpose LLMs continue to improve, fine-tuned methods on older models will not be able to compete to produce more accurate and efficient designs. Although some retrieval augmented generation (RAG) techniques exist to mitigate challenges presented in fine-tuning approaches, works tend to leverage low-quality codebases, incorporate computationally expensive fine-tuning in the frameworks, or do not use RAG directly in the RTL generation step. In this work, we introduce DeepV: a model-agnostic RAG framework to generate RTL designs by enhancing context through a large, high-quality dataset without any RTL-specific training. Our framework benefits the latest commercial LLM, OpenAI's GPT-5, with a near 17% increase in performance on the VerilogEval benchmark. We host DeepV for use by the community in a Hugging Face (HF) Space: https://huggingface.co/spaces/FICS-LLM/DeepV.