VeriGRAG: Enhancing LLM-Based Verilog Code Generation with Structure-Aware Soft Prompts

作者: Jiayu Zhao, Song Chen

分类: cs.AR, cs.AI, cs.PL

发布日期: 2025-09-27

备注: 9 pages, 5 figures

💡 一句话要点

VeriGRAG:利用结构感知软提示增强LLM的Verilog代码生成

🎯 匹配领域: 支柱九:具身大模型 (Embodied Foundation Models)

关键词: Verilog代码生成 大型语言模型 图神经网络 结构感知 软提示

📋 核心要点

- 现有方法难以有效利用Verilog代码中蕴含的硬件电路结构信息,导致LLM生成的代码在功能和语法上存在不足。

- VeriGRAG的核心思想是利用图神经网络提取Verilog代码的结构图嵌入,并将其融入到LLM的提示中,从而引导代码生成。

- 实验结果表明,VeriGRAG在VerilogEval和RTLLM基准测试中均取得了SOTA或更优的性能,显著提升了代码生成的正确性。

📝 摘要(中文)

大型语言模型(LLM)在从自然语言描述生成Verilog代码方面表现出强大的能力。然而,Verilog代码本质上编码了硬件电路的结构信息。如何有效地利用这种结构信息来提高LLM生成的Verilog代码的功能和语法正确性仍然是一个重大挑战。为了解决这个挑战,我们提出了VeriGRAG,这是一个新颖的框架,它使用图神经网络(GNN)从Verilog代码中提取结构图嵌入。然后,多模态检索器选择与给定生成任务最相关的图嵌入,并通过VeriFormer模块将其与代码模态对齐,以生成结构感知的软提示。我们的实验表明,VeriGRAG显著提高了Verilog代码生成的正确性,在VerilogEval和RTLLM基准测试中均实现了最先进或更优越的性能。

🔬 方法详解

问题定义:论文旨在解决LLM在生成Verilog代码时,无法有效利用硬件电路结构信息的问题。现有方法生成的代码在功能和语法上存在不足,难以满足实际需求。痛点在于如何将Verilog代码的结构信息有效地融入到LLM的生成过程中,从而提高代码的正确性和可靠性。

核心思路:论文的核心思路是利用图神经网络(GNN)提取Verilog代码的结构图嵌入,并将这些嵌入作为软提示(soft prompts)融入到LLM的生成过程中。通过这种方式,LLM可以感知到Verilog代码的结构信息,从而生成更符合硬件电路结构的代码。这样设计的目的是为了弥补LLM在处理结构化信息方面的不足,提高代码生成的质量。

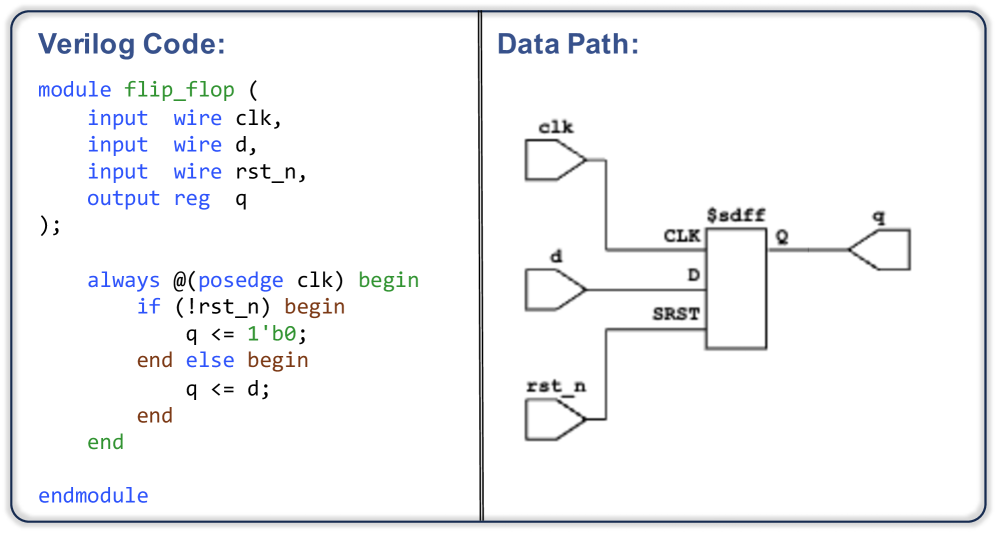

技术框架:VeriGRAG框架主要包含以下几个模块:1) 图神经网络(GNN):用于从Verilog代码中提取结构图嵌入。2) 多模态检索器:用于选择与给定生成任务最相关的图嵌入。3) VeriFormer模块:用于将图嵌入与代码模态对齐,生成结构感知的软提示。4) LLM:用于根据结构感知的软提示生成Verilog代码。整体流程是:首先,使用GNN提取Verilog代码的结构图嵌入;然后,使用多模态检索器选择相关的图嵌入;接着,使用VeriFormer模块生成软提示;最后,使用LLM生成Verilog代码。

关键创新:最重要的技术创新点在于提出了结构感知的软提示(structure-aware soft prompts)的概念,并将图神经网络提取的结构图嵌入融入到LLM的提示中。与现有方法相比,VeriGRAG能够更有效地利用Verilog代码的结构信息,从而提高代码生成的正确性和可靠性。现有方法通常只关注自然语言描述,忽略了Verilog代码的结构信息。

关键设计:论文中使用了图神经网络来提取Verilog代码的结构图嵌入,具体的GNN结构和参数设置未知。VeriFormer模块的具体实现细节未知,但其作用是将图嵌入与代码模态对齐。多模态检索器的具体实现细节也未知。损失函数的设计也未知,但其目标是提高代码生成的正确性和可靠性。

🖼️ 关键图片

📊 实验亮点

VeriGRAG在VerilogEval和RTLLM基准测试中均取得了最先进或更优越的性能,显著提高了Verilog代码生成的正确性。具体的性能提升幅度未知,但实验结果表明VeriGRAG能够有效地利用Verilog代码的结构信息,从而提高代码生成的质量。

🎯 应用场景

VeriGRAG具有广泛的应用前景,可以应用于自动化硬件设计、芯片验证、FPGA开发等领域。通过提高Verilog代码生成的质量和效率,可以缩短硬件开发周期,降低开发成本,并提高硬件系统的可靠性。未来,该技术有望进一步发展,实现更加智能化的硬件设计和验证。

📄 摘要(原文)

Large language models (LLMs) have demonstrated strong capabilities in generating Verilog code from natural language descriptions. However, Verilog code inherently encodes structural information of hardware circuits. Effectively leveraging this structural information to enhance the functional and syntactic correctness of LLM-generated Verilog code remains a significant challenge. To address this challenge, we propose VeriGRAG , a novel framework that extracts structural graph embeddings from Verilog code using graph neural networks (GNNs). A multimodal retriever then selects the graph embeddings most relevant to the given generation task, which are aligned with the code modality through the VeriFormer module to generate structure-aware soft prompts. Our experiments demonstrate that VeriGRAG substantially improves the correctness of Verilog code generation, achieving state-of-the-art or superior performance across both VerilogEval and RTLLM benchmarks.