EasySize: Elastic Analog Circuit Sizing via LLM-Guided Heuristic Search

作者: Xinyue Wu, Fan Hu, Shaik Jani Babu, Yi Zhao, Xinfei Guo

分类: cs.AI

发布日期: 2025-08-07

💡 一句话要点

EasySize:基于LLM引导的启发式搜索实现弹性模拟电路尺寸设计

🎯 匹配领域: 支柱二:RL算法与架构 (RL & Architecture) 支柱八:物理动画 (Physics-based Animation) 支柱九:具身大模型 (Embodied Foundation Models)

关键词: 模拟电路设计 门尺寸设计 大型语言模型 启发式搜索 差分进化 粒子群优化 Qwen3-8B 工艺节点

📋 核心要点

- 模拟电路门尺寸设计耗时且依赖经验,现有AI方法泛化性不足,且依赖大模型和特定工艺节点。

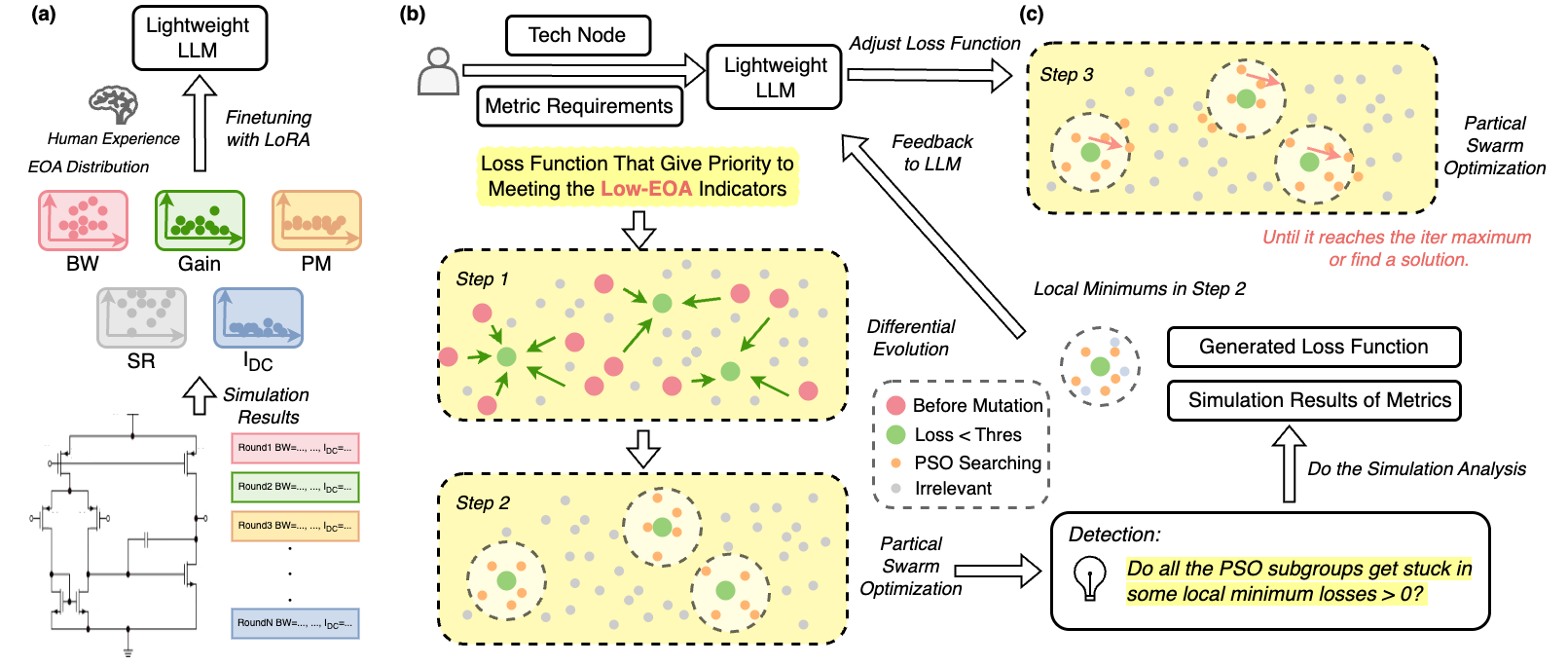

- EasySize利用微调的Qwen3-8B模型,根据性能指标易得性动态构建损失函数,结合全局DE和局部PSO进行高效搜索。

- EasySize在多种工艺节点和电路拓扑上表现出色,超越AutoCkt,并显著减少仿真资源消耗。

📝 摘要(中文)

模拟电路设计是芯片开发中耗时且依赖经验的任务。尽管人工智能取得了进展,但开发通用、快速和稳定的模拟电路门尺寸设计方法仍然是一个重大挑战。现有方法将大型语言模型(LLM)与启发式搜索技术相结合以增强通用性,但它们通常依赖于大型模型尺寸,并且缺乏跨不同技术节点的可移植性。为了克服这些限制,我们提出了EasySize,这是第一个基于微调的Qwen3-8B模型的轻量级门尺寸设计框架,专为跨工艺节点、设计规范和电路拓扑的通用适用性而设计。EasySize利用性能指标的不同易得性(EOA)来动态构建特定于任务的损失函数,从而通过全局差分进化(DE)和局部粒子群优化(PSO)在反馈增强流程中实现高效的启发式搜索。尽管仅在350nm节点数据上进行了微调,但EasySize在180nm、45nm和22nm技术节点的5个运算放大器(Op-Amp)网表上实现了强大的性能,无需额外的目标训练,并且在86.67%的任务上优于广泛使用的基于强化学习的尺寸设计框架AutoCkt,同时减少了96.67%以上的仿真资源。我们认为,EasySize可以显著减少门尺寸设计中对人工专业知识和计算资源的依赖,从而加速和简化模拟电路设计过程。EasySize将在稍后开源。

🔬 方法详解

问题定义:模拟电路的门尺寸设计是一个复杂且耗时的过程,需要大量的专业知识和计算资源。现有的基于AI的方法,特别是那些依赖于大型语言模型(LLM)的方法,虽然在一定程度上提高了自动化程度,但往往存在模型体积庞大、难以跨工艺节点移植以及训练成本高等问题。这些痛点限制了它们在实际工业应用中的普及。

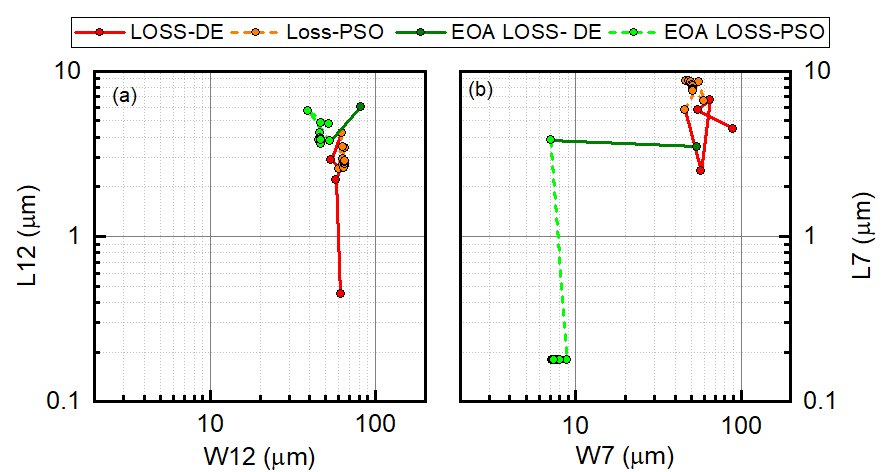

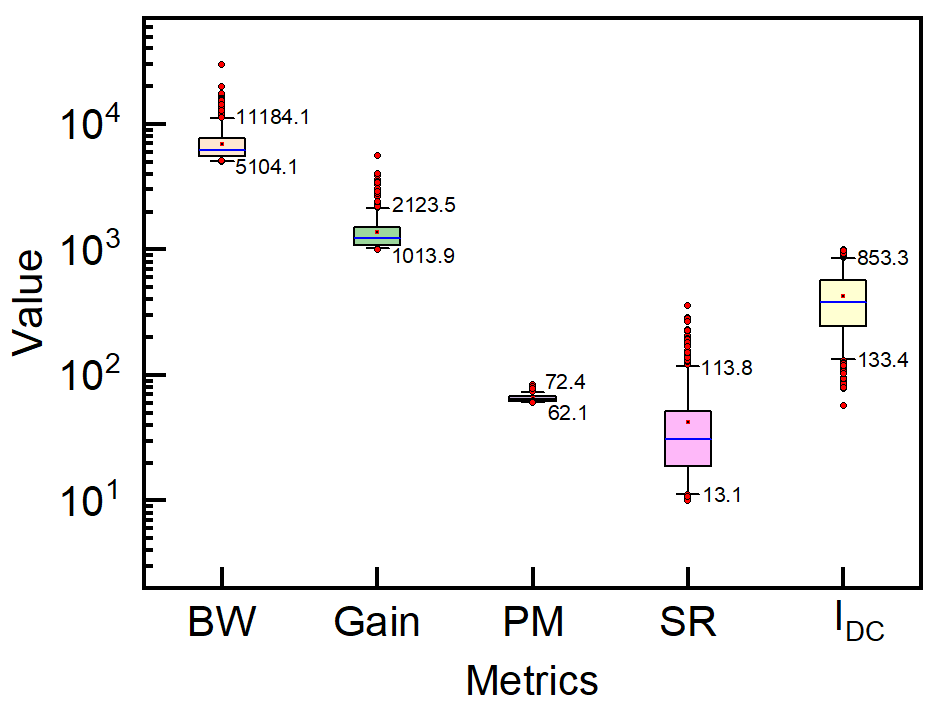

核心思路:EasySize的核心思路是利用一个轻量级的LLM(Qwen3-8B)作为先验知识的载体,并通过微调使其适应模拟电路设计任务。更重要的是,EasySize引入了“易得性(Ease of Attainability, EOA)”的概念,即不同性能指标的优化难度不同。基于EOA,EasySize动态地构建特定于任务的损失函数,从而引导启发式搜索过程,使其能够更有效地找到满足设计要求的门尺寸。

技术框架:EasySize的整体框架是一个反馈增强的启发式搜索流程。首先,使用微调后的Qwen3-8B模型初始化搜索空间。然后,利用全局差分进化(DE)算法进行初步的全局搜索,快速探索潜在的优化区域。接着,使用局部粒子群优化(PSO)算法对搜索结果进行精细调整,以获得更优的性能。在搜索过程中,根据电路仿真结果动态调整损失函数,形成一个闭环反馈系统。

关键创新:EasySize的关键创新在于其轻量级模型和动态损失函数构建方法。与依赖大型LLM的方法不同,EasySize使用微调后的Qwen3-8B模型,降低了计算成本和部署难度。同时,EOA驱动的动态损失函数能够根据不同性能指标的优化难度自适应地调整搜索策略,提高了搜索效率和成功率。这种方法使得EasySize能够在不同的工艺节点和电路拓扑上实现良好的泛化性能。

关键设计:EasySize的关键设计包括:1) 使用Qwen3-8B作为基础模型,并通过少量数据进行微调,使其适应模拟电路设计任务。2) 定义EOA指标,用于衡量不同性能指标的优化难度。3) 根据EOA动态构建损失函数,例如,对于难以优化的指标赋予更高的权重。4) 采用DE和PSO相结合的启发式搜索算法,DE用于全局探索,PSO用于局部优化。5) 构建反馈环路,根据仿真结果动态调整损失函数和搜索参数。

🖼️ 关键图片

📊 实验亮点

EasySize在多个工艺节点(180nm、45nm和22nm)的运算放大器设计任务上进行了评估,结果表明,即使仅在350nm节点数据上进行微调,EasySize也能在其他节点上取得良好的性能,无需额外的目标训练。与AutoCkt相比,EasySize在86.67%的任务上表现更优,并且减少了超过96.67%的仿真资源消耗。这些结果表明EasySize具有很强的泛化能力和高效性。

🎯 应用场景

EasySize具有广泛的应用前景,可用于加速各种模拟电路的设计过程,例如运算放大器、模数转换器、数模转换器等。它能够显著降低对人工经验的依赖,减少设计周期和成本,并提高电路性能。此外,EasySize的轻量级特性使其易于部署在不同的计算平台上,为模拟电路设计的自动化和智能化提供了新的解决方案。

📄 摘要(原文)

Analog circuit design is a time-consuming, experience-driven task in chip development. Despite advances in AI, developing universal, fast, and stable gate sizing methods for analog circuits remains a significant challenge. Recent approaches combine Large Language Models (LLMs) with heuristic search techniques to enhance generalizability, but they often depend on large model sizes and lack portability across different technology nodes. To overcome these limitations, we propose EasySize, the first lightweight gate sizing framework based on a finetuned Qwen3-8B model, designed for universal applicability across process nodes, design specifications, and circuit topologies. EasySize exploits the varying Ease of Attainability (EOA) of performance metrics to dynamically construct task-specific loss functions, enabling efficient heuristic search through global Differential Evolution (DE) and local Particle Swarm Optimization (PSO) within a feedback-enhanced flow. Although finetuned solely on 350nm node data, EasySize achieves strong performance on 5 operational amplifier (Op-Amp) netlists across 180nm, 45nm, and 22nm technology nodes without additional targeted training, and outperforms AutoCkt, a widely-used Reinforcement Learning based sizing framework, on 86.67\% of tasks with more than 96.67\% of simulation resources reduction. We argue that EasySize can significantly reduce the reliance on human expertise and computational resources in gate sizing, thereby accelerating and simplifying the analog circuit design process. EasySize will be open-sourced at a later date.