Hey AI, Generate Me a Hardware Code! Agentic AI-based Hardware Design & Verification

作者: Deepak Narayan Gadde, Keerthan Kopparam Radhakrishna, Vaisakh Naduvodi Viswambharan, Aman Kumar, Djones Lettnin, Wolfgang Kunz, Sebastian Simon

分类: cs.AI, cs.AR

发布日期: 2025-07-03

备注: To appear at the 38th SBC/SBMicro/IEEE Symposium on Integrated Circuits and Systems Design (SBCCI), August 25-29, 2025, Manaus, BRAZIL

DOI: 10.1109/SBCCI66862.2025.11218681

💡 一句话要点

提出基于Agentic AI的硬件设计与验证方法,提升效率和覆盖率。

🎯 匹配领域: 支柱九:具身大模型 (Embodied Foundation Models)

关键词: 硬件设计验证 Agentic AI 大型语言模型 人机协同 自动化验证

📋 核心要点

- 传统硬件设计验证流程繁琐耗时,难以保证无缺陷流片,成为集成电路开发的瓶颈。

- 利用大型语言模型(LLM)的强大能力,构建Agentic AI系统,实现硬件设计的自动化验证。

- 实验结果表明,该方法在覆盖率和验证时间上均优于传统方法,并具备良好的适应性和可配置性。

📝 摘要(中文)

现代集成电路(IC)日益复杂,其开发过程也是如此。硬件设计验证需要系统且规范的方法,对功能正确的硬件设计进行规划、开发、执行和最终确认。这个繁琐的过程需要大量精力和时间来确保无缺陷的流片。自然语言处理领域随着大型语言模型(LLM)的出现经历了重大变革。这些强大的模型,通常被称为生成式AI(GenAI),彻底改变了机器理解和生成人类语言的方式,从而在包括硬件设计验证在内的广泛应用中实现了前所未有的进步。本文提出了一种基于Agentic AI的硬件设计验证方法,该方法使AI Agent能够在人机协同(HITL)干预下,进行更动态、迭代和自反思的过程,最终执行端到端的硬件设计和验证。该方法在五个开源设计上进行了评估,实现了超过95%的覆盖率,同时减少了验证时间,并表现出卓越的性能、适应性和可配置性。

🔬 方法详解

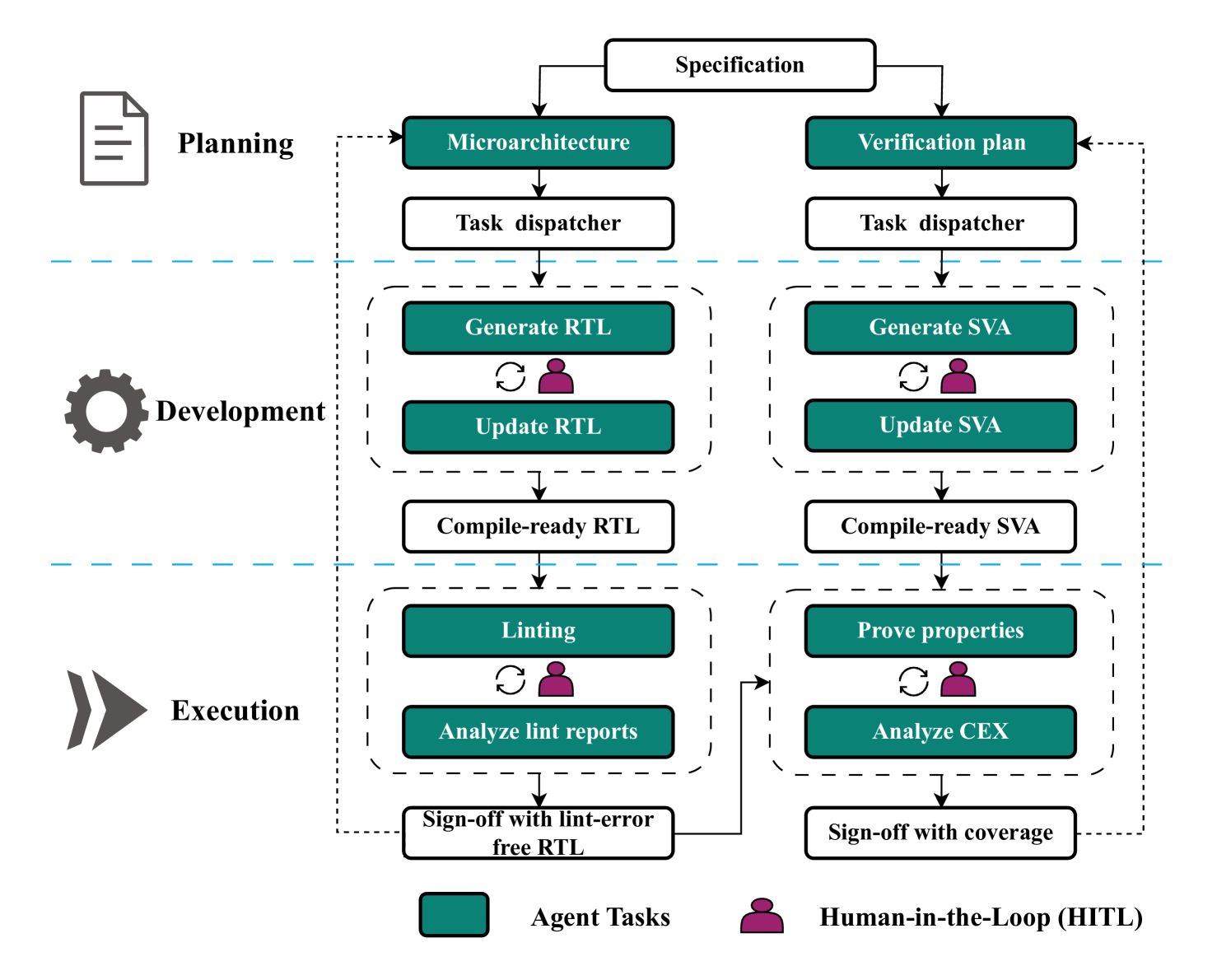

问题定义:论文旨在解决现代集成电路设计验证过程中耗时、易出错的问题。现有方法依赖人工编写测试用例,效率低下且难以覆盖所有潜在的错误。此外,随着芯片复杂度的增加,验证难度也呈指数级增长。

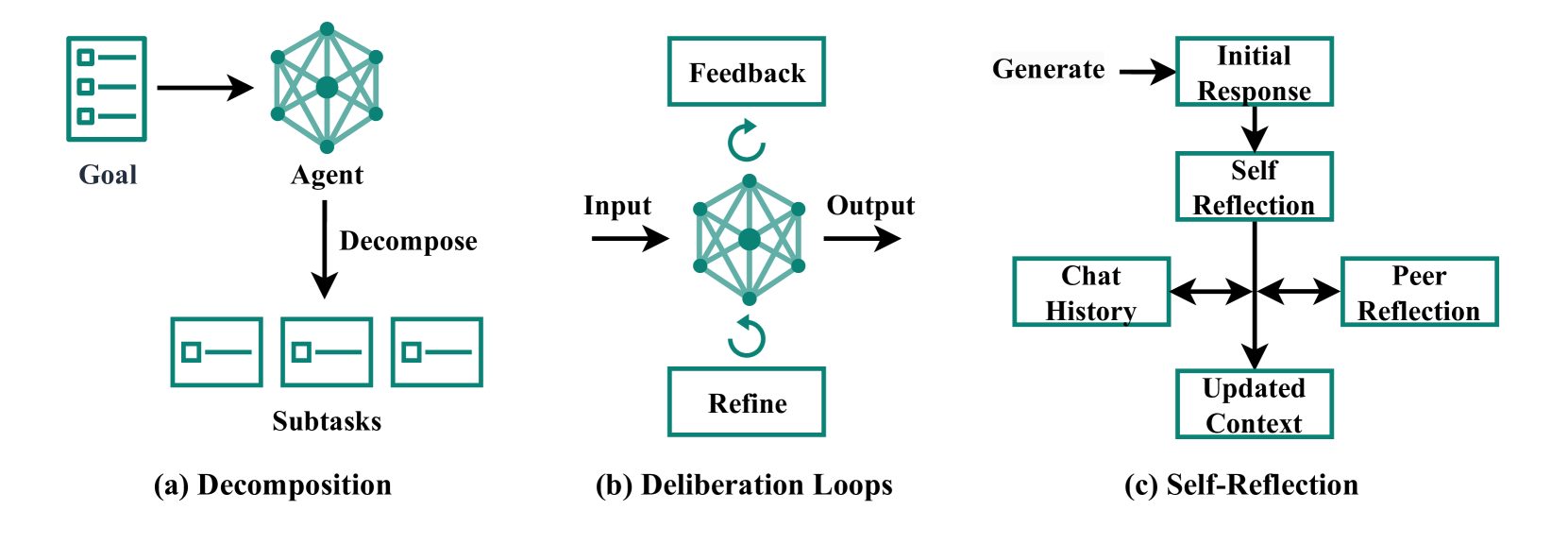

核心思路:论文的核心思路是利用大型语言模型(LLM)构建智能Agent,使其能够自主地进行硬件设计验证。通过人机协同(HITL)的方式,允许人工干预和指导Agent的行为,从而提高验证的效率和准确性。这种Agentic AI方法旨在模拟人类验证工程师的思考过程,自动生成测试用例、分析验证结果并进行迭代优化。

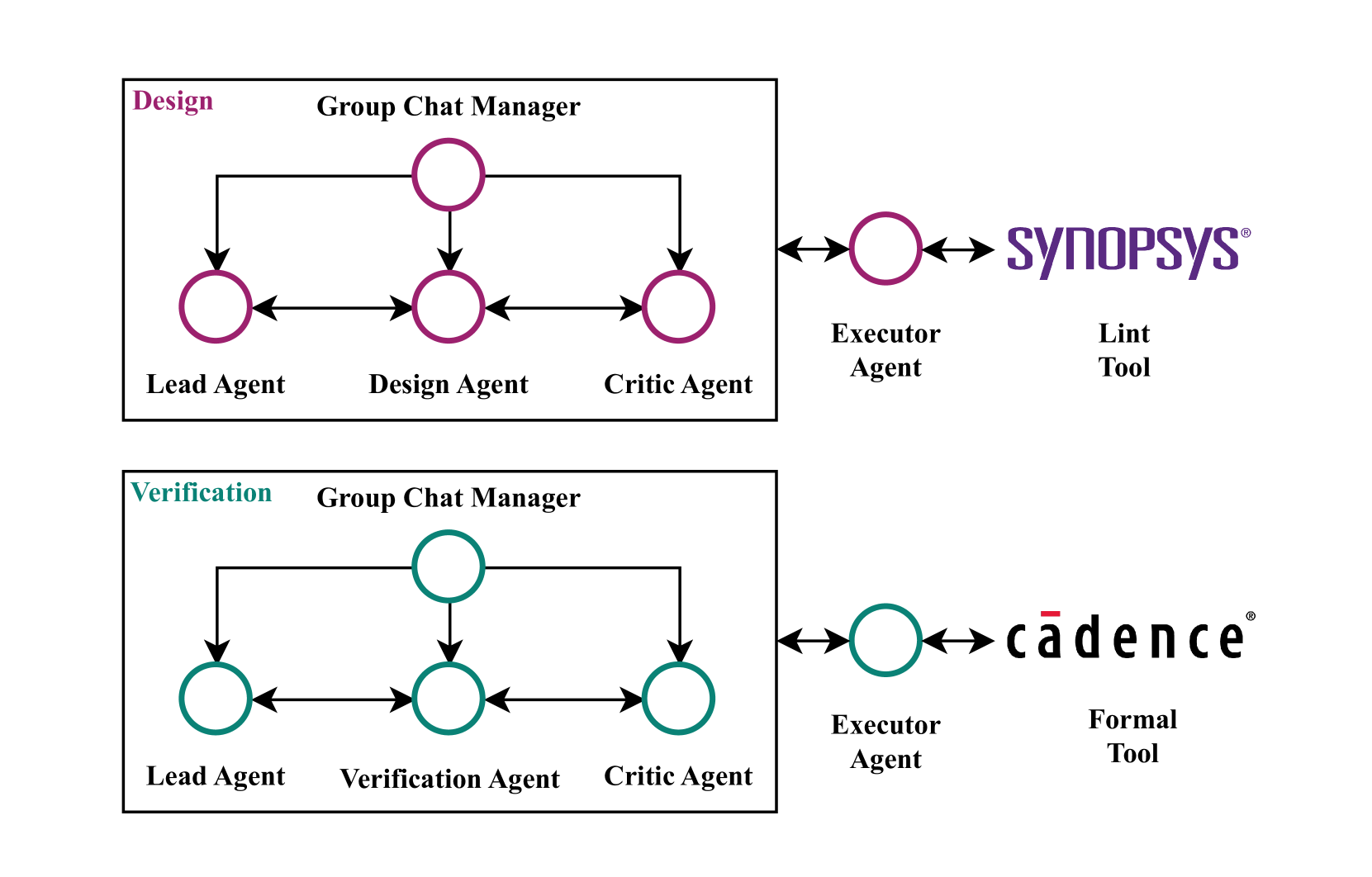

技术框架:该方法采用Agentic AI架构,包含以下主要模块:1) LLM驱动的Agent:负责理解硬件设计规范、生成测试用例、分析验证结果等。2) 验证环境:提供硬件设计的模拟环境,用于执行测试用例并收集验证结果。3) 人机协同接口:允许人工干预Agent的行为,例如提供指导、纠正错误等。4) 迭代优化模块:根据验证结果和人工反馈,不断优化Agent的策略和测试用例。

关键创新:该方法最重要的创新点在于将大型语言模型(LLM)应用于硬件设计验证领域,并构建了Agentic AI系统。与传统的基于规则或模型的验证方法相比,该方法具有更强的泛化能力和适应性,能够处理更复杂的硬件设计。此外,人机协同的方式也提高了验证的效率和准确性。

关键设计:论文中没有详细描述关键的参数设置、损失函数、网络结构等技术细节。但是,可以推断,LLM的选择和微调、Agent的奖励函数设计、人机协同接口的设计等都是关键的技术细节。具体实现可能依赖于特定的硬件设计语言和验证工具。

🖼️ 关键图片

📊 实验亮点

该方法在五个开源设计上进行了评估,实现了超过95%的覆盖率,同时减少了验证时间。实验结果表明,该方法在性能、适应性和可配置性方面均优于传统方法。这些结果表明,Agentic AI在硬件设计验证领域具有巨大的潜力。

🎯 应用场景

该研究成果可应用于各种集成电路的硬件设计验证,包括处理器、存储器、通信芯片等。通过自动化验证流程,可以显著缩短芯片的开发周期,降低开发成本,并提高芯片的质量和可靠性。未来,该技术有望进一步扩展到硬件设计的其他领域,例如自动生成硬件代码、自动优化硬件架构等。

📄 摘要(原文)

Modern Integrated Circuits (ICs) are becoming increasingly complex, and so is their development process. Hardware design verification entails a methodical and disciplined approach to the planning, development, execution, and sign-off of functionally correct hardware designs. This tedious process requires significant effort and time to ensure a bug-free tape-out. The field of Natural Language Processing has undergone a significant transformation with the advent of Large Language Models (LLMs). These powerful models, often referred to as Generative AI (GenAI), have revolutionized how machines understand and generate human language, enabling unprecedented advancements in a wide array of applications, including hardware design verification. This paper presents an agentic AI-based approach to hardware design verification, which empowers AI agents, in collaboration with Humain-in-the-Loop (HITL) intervention, to engage in a more dynamic, iterative, and self-reflective process, ultimately performing end-to-end hardware design and verification. This methodology is evaluated on five open-source designs, achieving over 95% coverage with reduced verification time while demonstrating superior performance, adaptability, and configurability.