SymRTLO: Enhancing RTL Code Optimization with LLMs and Neuron-Inspired Symbolic Reasoning

作者: Yiting Wang, Wanghao Ye, Ping Guo, Yexiao He, Ziyao Wang, Bowei Tian, Shwai He, Guoheng Sun, Zheyu Shen, Sihan Chen, Ankur Srivastava, Qingfu Zhang, Gang Qu, Ang Li

分类: cs.AR, cs.AI, cs.LG, cs.PL

发布日期: 2025-04-14 (更新: 2025-09-22)

备注: NeurIPS 2025

💡 一句话要点

SymRTLO:利用LLM和神经符号推理增强RTL代码优化

🎯 匹配领域: 支柱九:具身大模型 (Embodied Foundation Models)

关键词: RTL优化 大型语言模型 神经符号推理 形式验证 有限状态机 代码生成 硬件设计

📋 核心要点

- 现有RTL优化方法,如编译器优化和手动重写,在处理复杂约束和保证质量方面存在不足。

- SymRTLO结合LLM的代码生成能力与符号推理的严谨性,实现RTL代码的自动优化,同时保证正确性。

- 实验结果表明,SymRTLO在功耗、性能和面积上均优于现有方法,最高提升分别达到43.9%、62.5%和51.1%。

📝 摘要(中文)

优化寄存器传输级(RTL)代码对于提高数字电路在综合早期的功耗、性能和面积(PPA)至关重要。手动重写虽然质量高,但耗时且容易出错。现有基于编译器的方法难以处理复杂的设计约束。基于大型语言模型(LLM)的方法已成为一种有前景的替代方案。然而,LLM方法通常难以确保生成的代码与提供的提示对齐。本文提出了SymRTLO,一种新颖的神经符号RTL优化框架,它将基于LLM的代码重写与符号推理技术无缝集成。我们的方法结合了优化规则的检索增强生成(RAG)系统和基于抽象语法树(AST)的模板,实现了基于LLM的重写,既保持了语法正确性,又最大限度地减少了不良的电路行为。提出了一个符号模块,用于分析和优化有限状态机(FSM)逻辑,从而实现了超出基于模式的编译器的精细状态合并和部分规范处理。此外,一个快速验证管道,结合了形式等价性检查和测试驱动的验证,进一步降低了验证的复杂性。在RTL-Rewriter基准测试中使用Synopsys Design Compiler和Yosys进行的实验表明,与最先进的方法相比,SymRTLO在功耗、性能和面积(PPA)方面分别提高了高达43.9%、62.5%和51.1%。

🔬 方法详解

问题定义:论文旨在解决RTL代码优化问题,现有方法如编译器优化难以处理复杂约束,手动重写耗时易错。LLM虽然有潜力,但难以保证生成代码与prompt的一致性,可能引入错误或不期望的行为。

核心思路:核心思路是将LLM的代码生成能力与符号推理的严谨性相结合。利用LLM生成候选优化代码,然后通过符号推理验证和优化,确保代码的正确性和性能提升。这种神经符号结合的方式旨在克服LLM的局限性,并提高RTL优化的效率和质量。

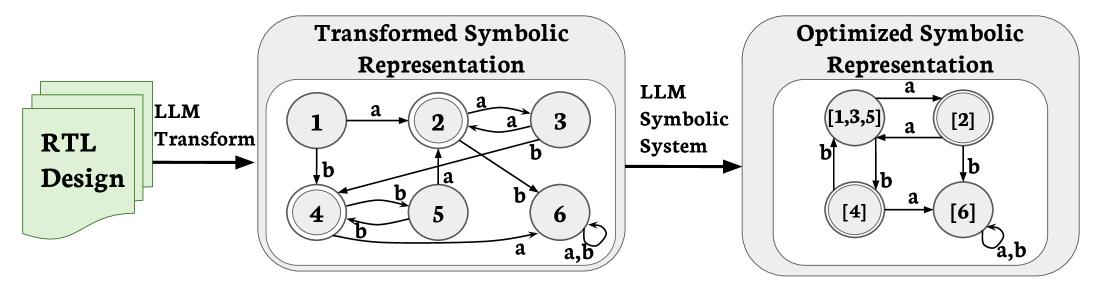

技术框架:SymRTLO框架包含三个主要模块:(1) 基于RAG的LLM代码重写模块,利用优化规则和AST模板生成候选代码;(2) 符号推理模块,用于分析和优化有限状态机(FSM)逻辑,进行状态合并等操作;(3) 快速验证管道,结合形式等价性检查和测试驱动的验证,确保优化后的代码功能正确。

关键创新:关键创新在于神经符号融合的RTL优化方法。具体来说,利用RAG和AST模板约束LLM的生成,保证语法正确性;引入符号推理模块,处理FSM优化等复杂逻辑;以及快速验证管道,降低验证成本。这种结合克服了传统方法和纯LLM方法的局限性。

关键设计:RAG模块的关键设计包括优化规则库的构建和AST模板的设计。符号推理模块的关键设计在于FSM状态合并算法和部分规范处理方法。快速验证管道的关键设计在于形式等价性检查工具的选择和测试用例的生成策略。论文中未明确说明具体的参数设置、损失函数或网络结构等细节,这部分内容可能属于商业机密或未在论文中详细展开。

🖼️ 关键图片

📊 实验亮点

实验结果表明,SymRTLO在RTL-Rewriter基准测试中,使用Synopsys Design Compiler和Yosys工具,与最先进的方法相比,在功耗、性能和面积(PPA)方面分别提高了高达43.9%、62.5%和51.1%。这些显著的提升证明了SymRTLO在RTL代码优化方面的有效性。

🎯 应用场景

SymRTLO可应用于数字电路设计的早期阶段,帮助工程师自动优化RTL代码,从而降低功耗、提高性能和减小芯片面积。该技术可集成到现有的EDA工具流程中,加速芯片设计周期,并提高芯片的整体质量和竞争力。未来,该方法有望扩展到更复杂的硬件设计优化问题。

📄 摘要(原文)

Optimizing Register Transfer Level (RTL) code is crucial for improving the power, performance, and area (PPA) of digital circuits in the early stages of synthesis. Manual rewriting, guided by synthesis feedback, can yield high-quality results but is time-consuming and error-prone. Most existing compiler-based approaches have difficulty handling complex design constraints. Large Language Model (LLM)-based methods have emerged as a promising alternative to address these challenges. However, LLM-based approaches often face difficulties in ensuring alignment between the generated code and the provided prompts. This paper presents SymRTLO, a novel neuron-symbolic RTL optimization framework that seamlessly integrates LLM-based code rewriting with symbolic reasoning techniques. Our method incorporates a retrieval-augmented generation (RAG) system of optimization rules and Abstract Syntax Tree (AST)-based templates, enabling LLM-based rewriting that maintains syntactic correctness while minimizing undesired circuit behaviors. A symbolic module is proposed for analyzing and optimizing finite state machine (FSM) logic, allowing fine-grained state merging and partial specification handling beyond the scope of pattern-based compilers. Furthermore, a fast verification pipeline, combining formal equivalence checks with test-driven validation, further reduces the complexity of verification. Experiments on the RTL-Rewriter benchmark with Synopsys Design Compiler and Yosys show that SymRTLO improves power, performance, and area (PPA) by up to 43.9%, 62.5%, and 51.1%, respectively, compared to the state-of-the-art methods.