AIvril: AI-Driven RTL Generation With Verification In-The-Loop

作者: Mubashir ul Islam, Humza Sami, Pierre-Emmanuel Gaillardon, Valerio Tenace

分类: cs.AI, cs.AR, cs.CL, cs.LG, cs.MA

发布日期: 2024-09-03

💡 一句话要点

AIvril:一种AI驱动的RTL生成框架,具有环路验证机制,显著提升代码质量。

🎯 匹配领域: 支柱九:具身大模型 (Embodied Foundation Models)

关键词: RTL生成 大语言模型 硬件设计 自动验证 多智能体系统

📋 核心要点

- 现有大语言模型在RTL生成中存在不准确的问题,这在对可靠性和精度要求极高的硬件设计领域是一个重大缺陷。

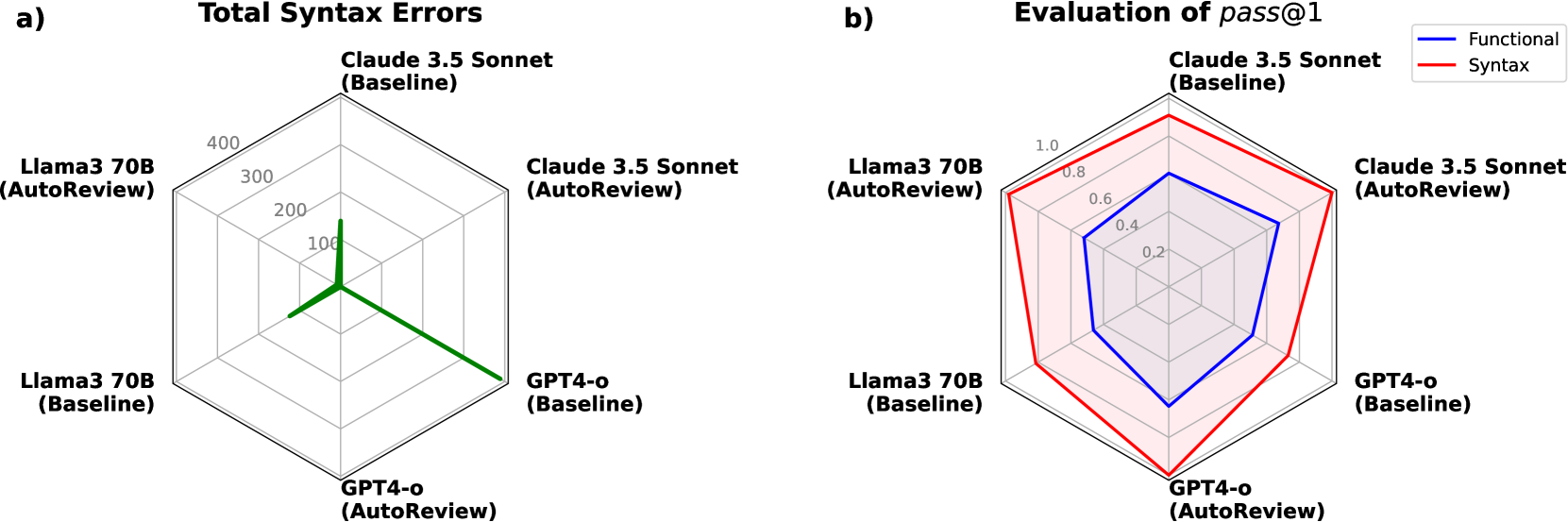

- AIvril框架采用多智能体系统,独立于底层LLM,通过自动语法纠正和功能验证来提升RTL代码生成的准确性和可靠性。

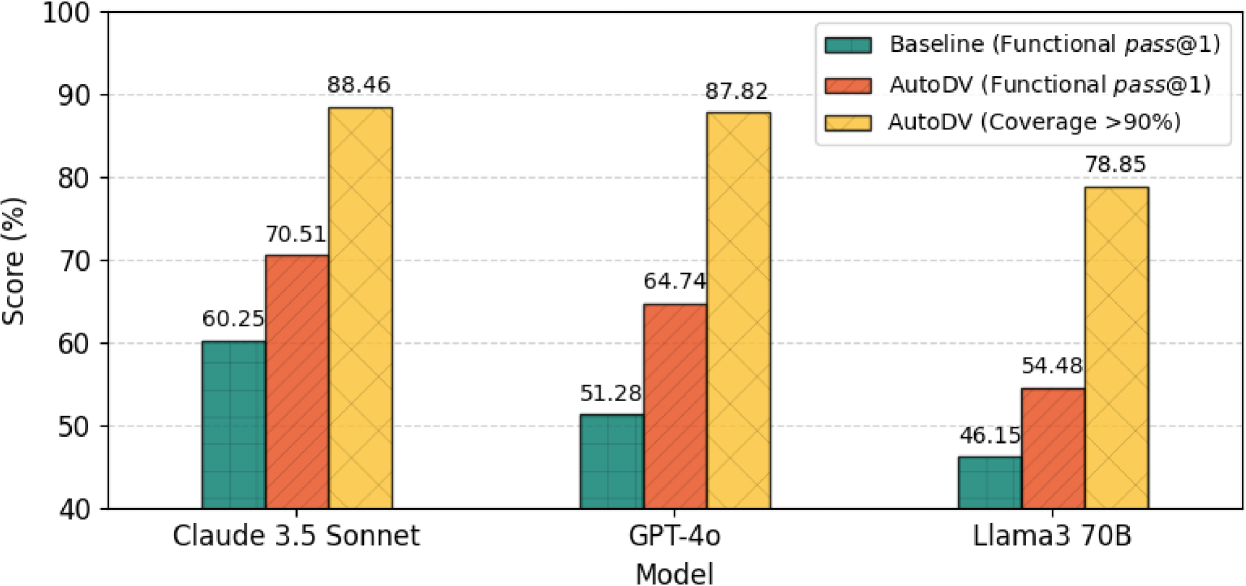

- 实验表明,AIvril在VerilogEval-Human数据集上将代码质量提升近2倍,验证目标的成功率达到88.46%。

📝 摘要(中文)

本文介绍了一种名为AIvril的先进框架,旨在提高RTL(寄存器传输级)感知的大语言模型(LLM)的准确性和可靠性。AIvril采用多智能体、与LLM无关的系统,用于自动语法纠正和功能验证,从而显著减少甚至完全消除错误代码生成的情况。在VerilogEval-Human数据集上进行的实验结果表明,与之前的工作相比,我们的框架将代码质量提高了近2倍,同时在满足验证目标方面实现了88.46%的成功率。这代表着在自动化和优化硬件设计工作流程方面迈出了关键一步,为AI驱动的RTL设计提供了一种更可靠的方法。

🔬 方法详解

问题定义:论文旨在解决大语言模型(LLM)在寄存器传输级(RTL)代码生成中存在的准确性和可靠性问题。现有方法生成的RTL代码容易出现语法错误和功能错误,这对于硬件设计来说是不可接受的,因为硬件设计的正确性至关重要。

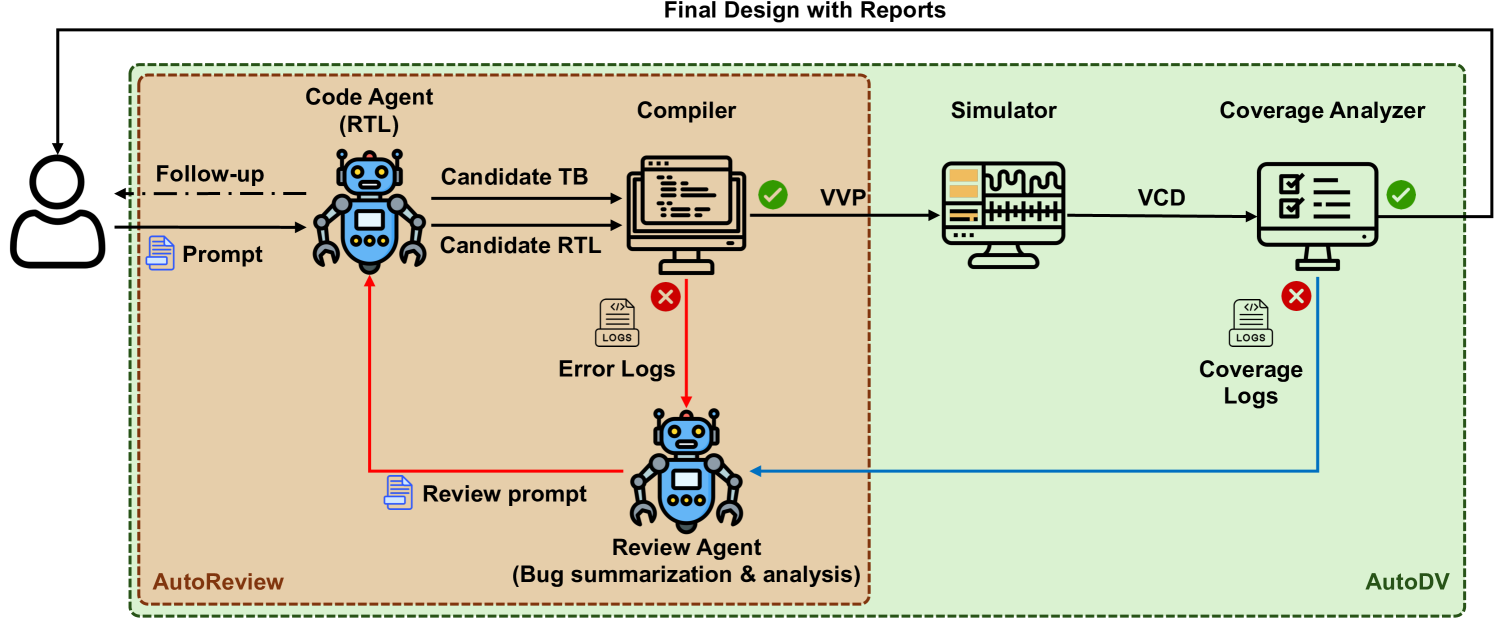

核心思路:AIvril的核心思路是引入一个多智能体系统,该系统能够自动检测和纠正LLM生成的RTL代码中的语法错误,并进行功能验证,以确保生成的代码符合设计规范。这种方法通过在生成过程中加入验证环节,从而提高最终RTL代码的质量。

技术框架:AIvril框架包含多个智能体,这些智能体协同工作以完成RTL代码的生成和验证。主要模块包括:LLM代码生成器(负责生成初始RTL代码),语法纠正器(负责检测和修复代码中的语法错误),功能验证器(负责验证代码的功能是否符合预期),以及一个协调这些智能体的控制器。整个流程是一个迭代过程,直到代码通过所有验证。

关键创新:AIvril的关键创新在于其多智能体架构和环路验证机制。与传统的单次生成方法不同,AIvril通过迭代的验证和纠正过程,显著提高了RTL代码的质量。此外,AIvril的设计与底层LLM无关,这意味着它可以与各种不同的LLM集成使用。

关键设计:AIvril的关键设计包括:语法纠正器的具体实现(例如,使用基于规则的方法或基于机器学习的方法),功能验证器的验证策略(例如,使用形式验证或仿真验证),以及智能体之间的通信和协调机制。具体的参数设置和损失函数取决于所使用的具体技术,论文中可能没有详细说明。

🖼️ 关键图片

📊 实验亮点

实验结果表明,AIvril框架在VerilogEval-Human数据集上取得了显著的性能提升。与之前的工作相比,AIvril将RTL代码质量提高了近2倍,并且在满足验证目标方面实现了88.46%的成功率。这些数据表明,AIvril是一种有效的RTL代码生成和验证方法。

🎯 应用场景

AIvril框架可应用于各种硬件设计领域,包括处理器设计、存储器设计、网络芯片设计等。通过自动化RTL代码生成和验证,它可以显著缩短硬件设计周期,降低设计成本,并提高硬件产品的质量和可靠性。未来,AIvril有望成为硬件设计工程师的重要工具,推动硬件设计的智能化和自动化。

📄 摘要(原文)

Large Language Models (LLMs) are computational models capable of performing complex natural language processing tasks. Leveraging these capabilities, LLMs hold the potential to transform the entire hardware design stack, with predictions suggesting that front-end and back-end tasks could be fully automated in the near future. Currently, LLMs show great promise in streamlining Register Transfer Level (RTL) generation, enhancing efficiency, and accelerating innovation. However, their probabilistic nature makes them prone to inaccuracies - a significant drawback in RTL design, where reliability and precision are essential. To address these challenges, this paper introduces AIvril, an advanced framework designed to enhance the accuracy and reliability of RTL-aware LLMs. AIvril employs a multi-agent, LLM-agnostic system for automatic syntax correction and functional verification, significantly reducing - and in many cases, completely eliminating - instances of erroneous code generation. Experimental results conducted on the VerilogEval-Human dataset show that our framework improves code quality by nearly 2x when compared to previous works, while achieving an 88.46% success rate in meeting verification objectives. This represents a critical step toward automating and optimizing hardware design workflows, offering a more dependable methodology for AI-driven RTL design.