Natural language is not enough: Benchmarking multi-modal generative AI for Verilog generation

作者: Kaiyan Chang, Zhirong Chen, Yunhao Zhou, Wenlong Zhu, kun wang, Haobo Xu, Cangyuan Li, Mengdi Wang, Shengwen Liang, Huawei Li, Yinhe Han, Ying Wang

分类: cs.AR, cs.AI

发布日期: 2024-07-11

备注: Accepted by ICCAD 2024

💡 一句话要点

提出多模态生成AI框架,提升Verilog代码生成精度,解决自然语言描述硬件设计不足问题。

🎯 匹配领域: 支柱九:具身大模型 (Embodied Foundation Models)

关键词: Verilog生成 多模态学习 硬件设计自动化 视觉语言模型 代码生成

📋 核心要点

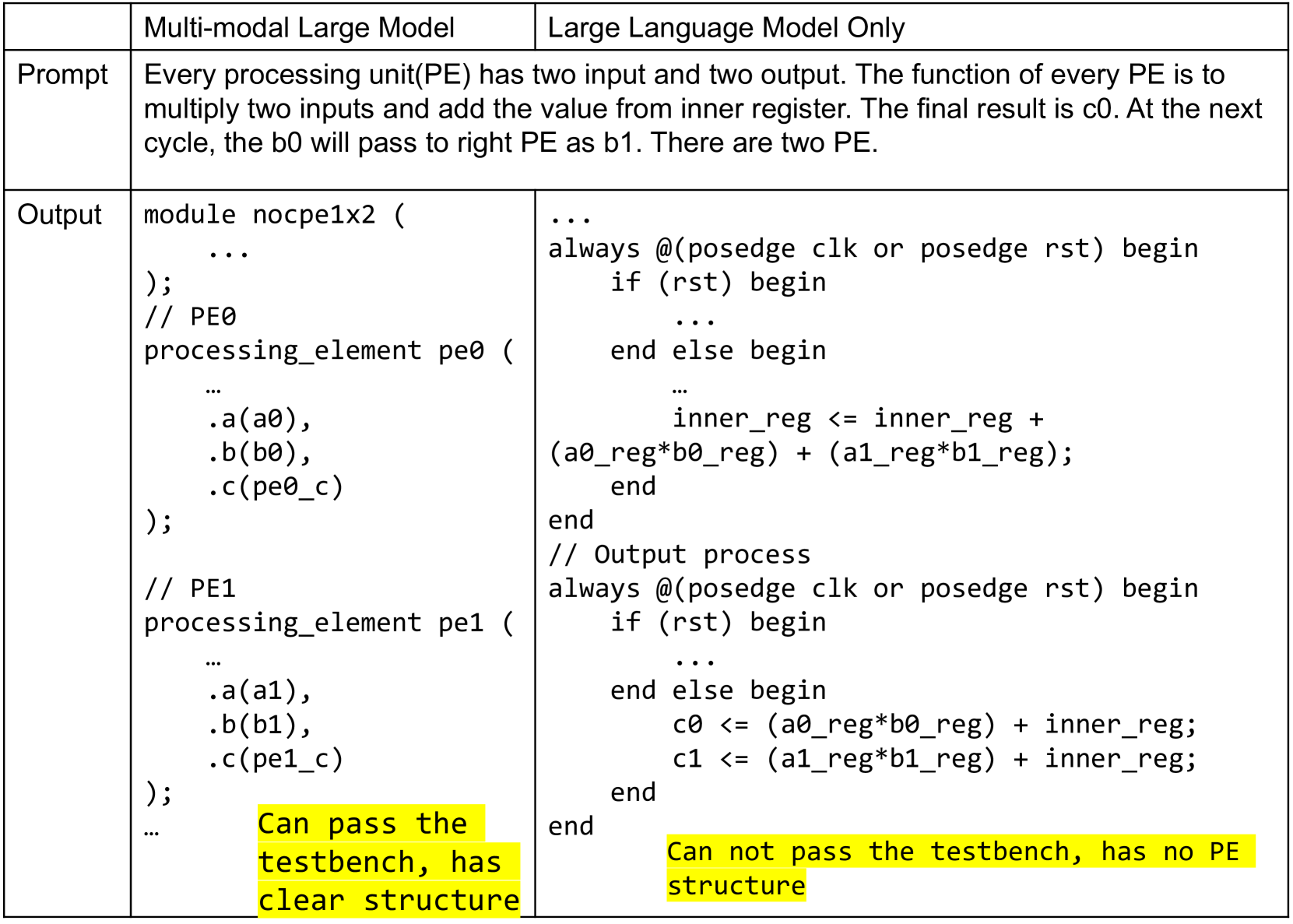

- 现有方法仅依赖自然语言生成Verilog代码,忽略了硬件设计中重要的视觉上下文信息,导致生成精度受限。

- 论文提出一种多模态生成AI框架,结合视觉和语言信息,更准确地捕捉硬件设计的意图,提升代码生成质量。

- 实验结果表明,相比于仅使用自然语言的方法,该多模态方法在Verilog生成任务中取得了显著的准确率提升。

📝 摘要(中文)

本文提出了一种基于多模态生成AI的Verilog代码生成方法,旨在解决仅依赖自然语言描述硬件设计意图的局限性。研究表明,视觉信息对于具有空间复杂性的硬件架构至关重要。为此,论文构建了一个开源的视觉-语言Verilog综合基准,用于评估单模块和复杂模块的生成效果。同时,论文还提出了一个开源的视觉和自然语言Verilog查询语言框架,以方便用户进行多模态查询。实验结果表明,相比于仅使用自然语言的方法,多模态方法在Verilog生成任务中显著提高了准确性。该研究为大硬件设计模型时代提供了一种新的硬件设计方法。

🔬 方法详解

问题定义:现有Verilog代码生成方法主要依赖于自然语言描述,这种方法忽略了硬件设计中重要的视觉信息,尤其是在描述具有复杂空间结构的硬件架构时,自然语言的表达能力存在局限性。因此,如何有效地利用视觉信息来辅助Verilog代码生成,提高生成代码的准确性和完整性,是本文要解决的核心问题。

核心思路:论文的核心思路是将视觉信息与自然语言信息相结合,构建一个多模态的生成模型。通过引入视觉信息,模型可以更好地理解硬件设计的空间结构和连接关系,从而更准确地生成Verilog代码。这种方法旨在弥补自然语言描述的不足,提高生成代码的质量。

技术框架:该多模态Verilog生成框架包含以下几个主要模块:1) 视觉信息编码模块:用于提取硬件设计的视觉特征,例如电路图的结构信息。2) 自然语言信息编码模块:用于提取自然语言描述的语义信息。3) 多模态融合模块:将视觉特征和语义信息进行融合,得到一个综合的表示。4) Verilog代码生成模块:基于融合后的表示,生成Verilog代码。此外,论文还提出了一个视觉和自然语言Verilog查询语言框架,方便用户进行多模态查询。

关键创新:论文的关键创新在于提出了一个多模态的Verilog代码生成方法,将视觉信息引入到代码生成过程中。与传统的仅依赖自然语言的方法相比,该方法能够更准确地捕捉硬件设计的意图,从而生成更准确、更完整的Verilog代码。此外,开源的视觉-语言Verilog综合基准和查询语言框架也为后续研究提供了便利。

关键设计:论文中没有详细描述具体的网络结构、损失函数或参数设置。但是,可以推断,视觉信息编码模块可能采用卷积神经网络(CNN)来提取图像特征,自然语言信息编码模块可能采用Transformer等模型来提取语义信息。多模态融合模块可能采用注意力机制等方法来实现视觉和语言信息的有效融合。Verilog代码生成模块可能采用序列到序列(Seq2Seq)模型或Transformer等模型来生成代码。

🖼️ 关键图片

📊 实验亮点

实验结果表明,该多模态方法在Verilog生成任务中显著提高了准确性,优于仅使用自然语言的方法。具体的性能数据和提升幅度需要在论文中查找。该结果验证了视觉信息在硬件设计中的重要性,并为多模态硬件设计提供了一种新的思路。

🎯 应用场景

该研究成果可应用于自动化硬件设计流程,降低硬件开发门槛,提高设计效率。例如,工程师可以通过简单的电路图和自然语言描述,快速生成Verilog代码,从而加速硬件原型设计和验证。此外,该技术还可用于教育领域,帮助学生更好地理解硬件设计原理。

📄 摘要(原文)

Natural language interfaces have exhibited considerable potential in the automation of Verilog generation derived from high-level specifications through the utilization of large language models, garnering significant attention. Nevertheless, this paper elucidates that visual representations contribute essential contextual information critical to design intent for hardware architectures possessing spatial complexity, potentially surpassing the efficacy of natural-language-only inputs. Expanding upon this premise, our paper introduces an open-source benchmark for multi-modal generative models tailored for Verilog synthesis from visual-linguistic inputs, addressing both singular and complex modules. Additionally, we introduce an open-source visual and natural language Verilog query language framework to facilitate efficient and user-friendly multi-modal queries. To evaluate the performance of the proposed multi-modal hardware generative AI in Verilog generation tasks, we compare it with a popular method that relies solely on natural language. Our results demonstrate a significant accuracy improvement in the multi-modal generated Verilog compared to queries based solely on natural language. We hope to reveal a new approach to hardware design in the large-hardware-design-model era, thereby fostering a more diversified and productive approach to hardware design.