LLM-Enhanced Bayesian Optimization for Efficient Analog Layout Constraint Generation

作者: Guojin Chen, Keren Zhu, Seunggeun Kim, Hanqing Zhu, Yao Lai, Bei Yu, David Z. Pan

分类: cs.AI, cs.AR, cs.LG

发布日期: 2024-06-07 (更新: 2024-12-06)

🔗 代码/项目: GITHUB

💡 一句话要点

提出LLANA框架,利用LLM增强贝叶斯优化,高效生成模拟版图约束。

🎯 匹配领域: 支柱九:具身大模型 (Embodied Foundation Models)

关键词: 模拟版图综合 贝叶斯优化 大型语言模型 少样本学习 电路设计

📋 核心要点

- 模拟版图综合依赖手动调整,耗时且性能不稳定,现有基于贝叶斯优化的方法存在收敛慢、数据需求大的问题。

- LLANA框架利用大型语言模型的少样本学习能力,辅助贝叶斯优化,高效生成模拟设计相关的参数约束。

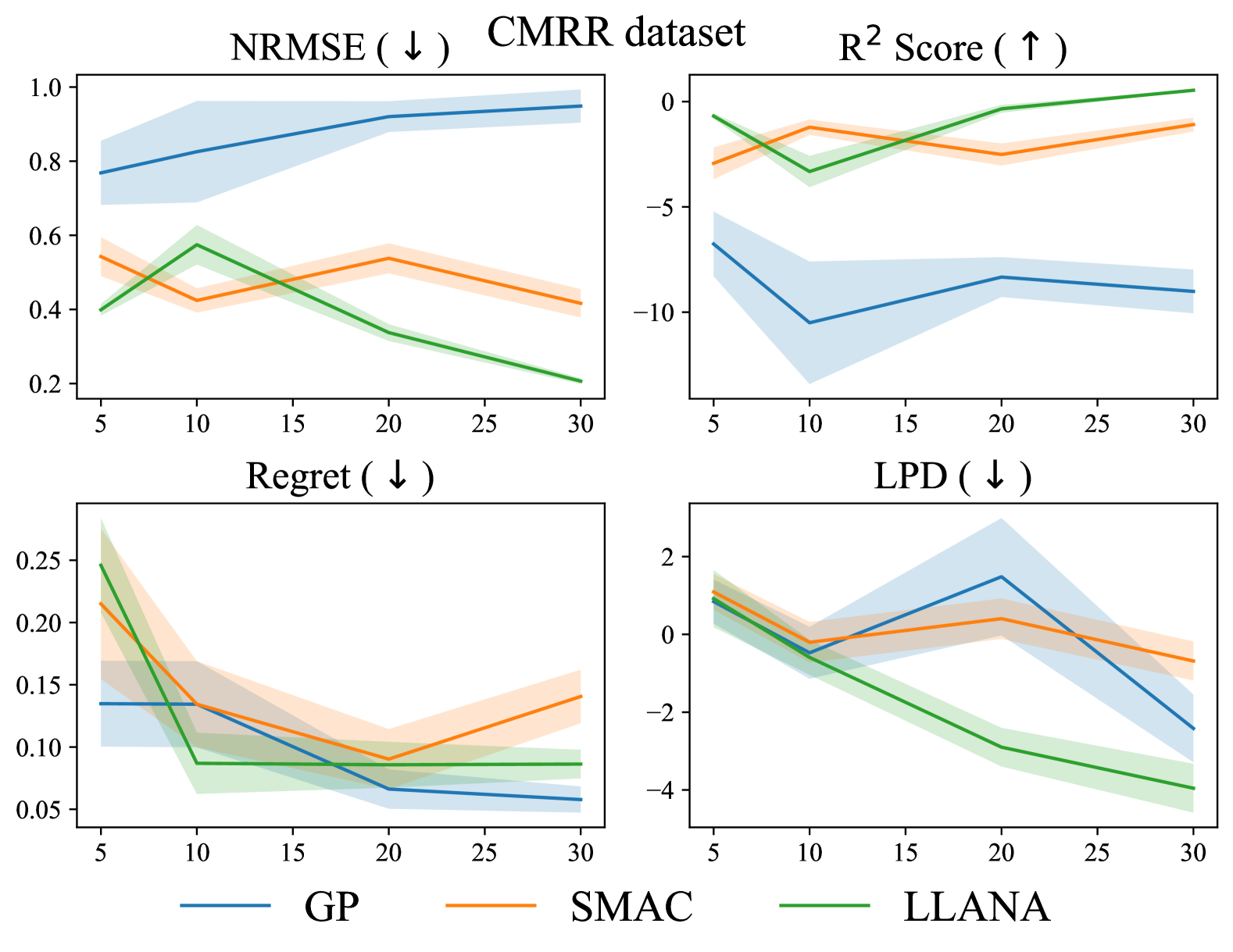

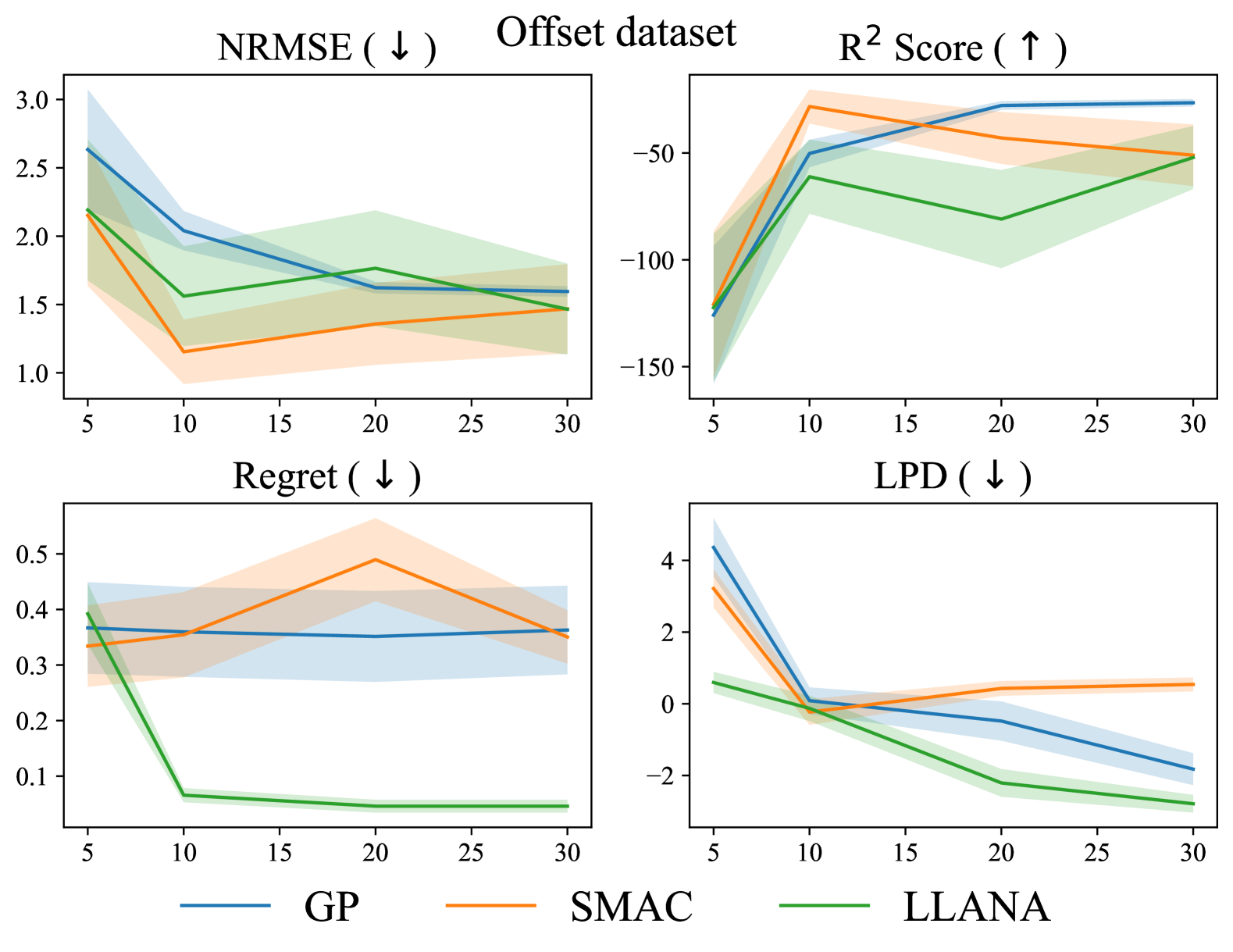

- 实验结果表明,LLANA在性能上可与SOTA的BO方法媲美,并能更有效地探索模拟电路设计空间。

📝 摘要(中文)

模拟版图综合面临手动流程依赖、耗时和性能不稳定等挑战。现有的基于贝叶斯优化(BO)的技术虽然有自动化的潜力,但收敛速度慢、数据需求大,限制了实际应用。本文提出了 exttt{LLANA}框架,这是一种利用大型语言模型(LLM)增强BO的新方法,通过利用LLM的少样本学习能力,更有效地生成模拟设计相关的参数约束。实验结果表明, exttt{LLANA}不仅实现了与最先进(SOTA)的BO方法相当的性能,而且由于LLM卓越的上下文理解和学习效率,能够更有效地探索模拟电路设计空间。代码可在https://github.com/dekura/LLANA获取。

🔬 方法详解

问题定义:模拟版图综合的自动化程度低,依赖人工经验,耗时且容易出错。现有的基于贝叶斯优化的方法虽然可以实现自动化,但需要大量的训练数据才能达到较好的性能,收敛速度慢,难以满足实际应用的需求。因此,如何减少数据需求,加速收敛,是当前模拟版图综合面临的关键问题。

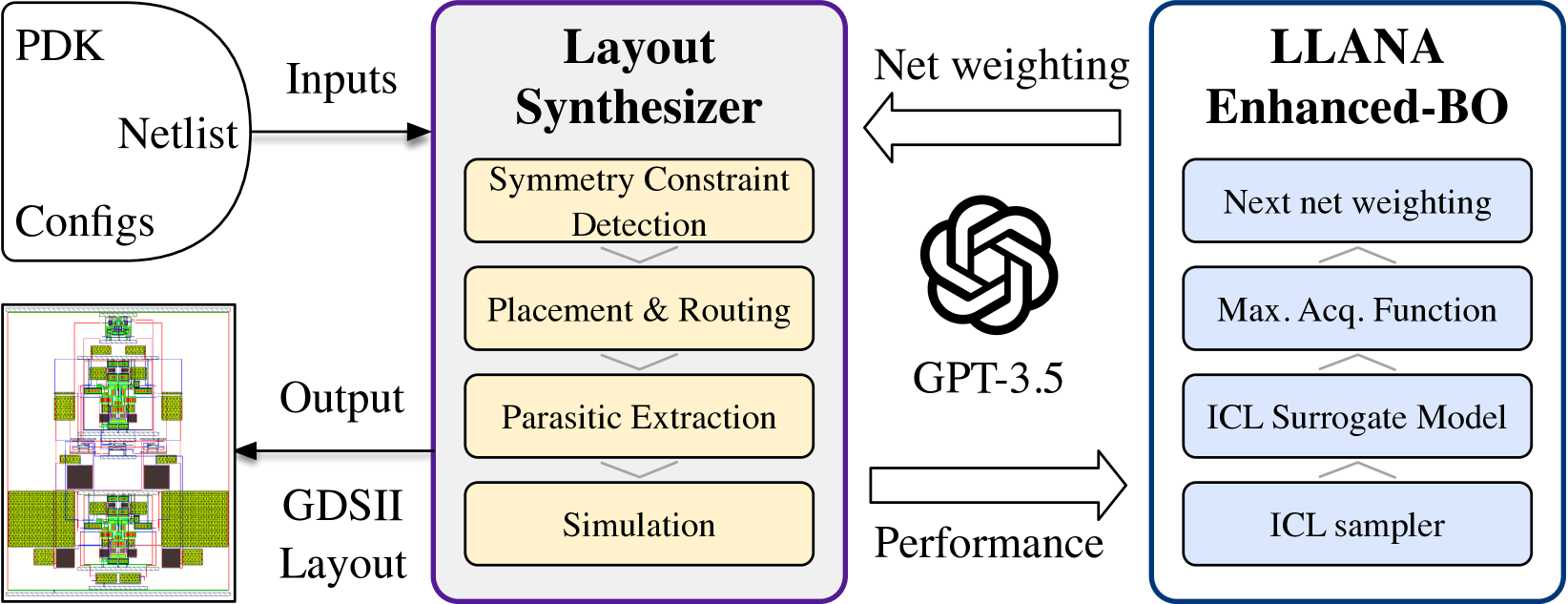

核心思路:论文的核心思路是利用大型语言模型(LLM)的上下文理解和少样本学习能力,辅助贝叶斯优化过程。LLM可以从少量数据中学习到模拟电路设计的规律,从而为贝叶斯优化提供更好的先验知识,指导其更有效地探索设计空间,减少无效的搜索,加速收敛。

技术框架:LLANA框架主要包含以下几个模块:1) 数据收集模块:收集少量模拟电路设计的参数和性能数据;2) LLM训练模块:利用收集到的数据训练LLM,使其学习到模拟电路设计的规律;3) 贝叶斯优化模块:利用训练好的LLM作为先验知识,指导贝叶斯优化过程,生成模拟版图约束;4) 评估模块:评估生成的约束的性能,并反馈给贝叶斯优化模块,进行迭代优化。

关键创新:LLANA框架的关键创新在于将大型语言模型引入到模拟版图综合中,利用LLM的少样本学习能力,解决了传统贝叶斯优化方法数据需求大的问题。与现有方法相比,LLANA框架可以从更少的数据中学习到模拟电路设计的规律,从而更有效地探索设计空间,加速收敛。

关键设计:LLM的具体选择和训练方式未知,论文中可能使用了某种特定的LLM架构和训练策略。贝叶斯优化模块可能使用了某种特定的采集函数和高斯过程模型。这些技术细节需要在论文中进一步查找。

🖼️ 关键图片

📊 实验亮点

实验结果表明,LLANA框架在模拟版图约束生成方面取得了与SOTA的BO方法相当的性能,同时显著减少了数据需求,提高了探索设计空间的效率。具体性能数据和对比基线未知,需要在论文中进一步查找。

🎯 应用场景

该研究成果可应用于模拟集成电路的自动版图生成,能够显著缩短设计周期,降低设计成本,提高设计效率。通过LLM的辅助,即使缺乏经验的设计师也能快速生成高质量的模拟版图,加速芯片的开发和上市。未来,该方法有望推广到其他类型的电路设计中,实现更广泛的自动化。

📄 摘要(原文)

Analog layout synthesis faces significant challenges due to its dependence on manual processes, considerable time requirements, and performance instability. Current Bayesian Optimization (BO)-based techniques for analog layout synthesis, despite their potential for automation, suffer from slow convergence and extensive data needs, limiting their practical application. This paper presents the \texttt{LLANA} framework, a novel approach that leverages Large Language Models (LLMs) to enhance BO by exploiting the few-shot learning abilities of LLMs for more efficient generation of analog design-dependent parameter constraints. Experimental results demonstrate that \texttt{LLANA} not only achieves performance comparable to state-of-the-art (SOTA) BO methods but also enables a more effective exploration of the analog circuit design space, thanks to LLM's superior contextual understanding and learning efficiency. The code is available at https://github.com/dekura/LLANA.