VHDL-Eval: A Framework for Evaluating Large Language Models in VHDL Code Generation

作者: Prashanth Vijayaraghavan, Luyao Shi, Stefano Ambrogio, Charles Mackin, Apoorva Nitsure, David Beymer, Ehsan Degan

分类: cs.SE, cs.AI, cs.CL

发布日期: 2024-06-06

备注: 6 pages, 3 Figures, LAD'24

💡 一句话要点

VHDL-Eval:构建VHDL代码生成LLM评估框架,揭示现有模型的局限性。

🎯 匹配领域: 支柱九:具身大模型 (Embodied Foundation Models)

关键词: VHDL代码生成 大型语言模型 评估框架 硬件描述语言 代码生成 自验证测试平台 数据集构建

📋 核心要点

- 现有LLM在通用编程语言代码生成方面取得了显著进展,但在硬件描述语言(HDL)特别是VHDL方面缺乏全面的评估框架。

- 论文构建了一个专门针对VHDL代码生成的评估框架VHDL-Eval,包含数据集和评估方法,用于系统性地评估LLM在VHDL代码生成任务中的表现。

- 实验结果表明,现有LLM在VHDL代码生成方面表现不佳,凸显了针对VHDL进行专门微调的必要性,并为未来的研究方向提供了指导。

📝 摘要(中文)

本文提出一个全面的评估框架,专门用于评估大型语言模型(LLM)在VHDL代码生成任务中的性能。通过将Verilog评估问题翻译成VHDL,并整合公开可用的VHDL问题,构建了一个包含202个问题的VHDL代码生成数据集。为了评估生成VHDL代码的功能正确性,利用了一组专门为此问题集设计的自验证测试平台。对不同的LLM及其变体进行了初步评估,包括零样本代码生成、上下文学习(ICL)和参数高效微调(PEFT)方法。研究结果表明,现有的LLM在VHDL代码生成方面面临着巨大的挑战,存在很大的改进空间。这项研究强调了针对VHDL进行监督微调代码生成模型的必要性,为寻求高效代码生成解决方案的VHDL设计人员提供了潜在的益处。

🔬 方法详解

问题定义:论文旨在解决缺乏针对VHDL代码生成的大型语言模型(LLM)评估框架的问题。现有方法主要集中在通用编程语言的代码生成,忽略了硬件描述语言的特殊性和挑战,导致无法有效评估LLM在VHDL代码生成方面的能力。

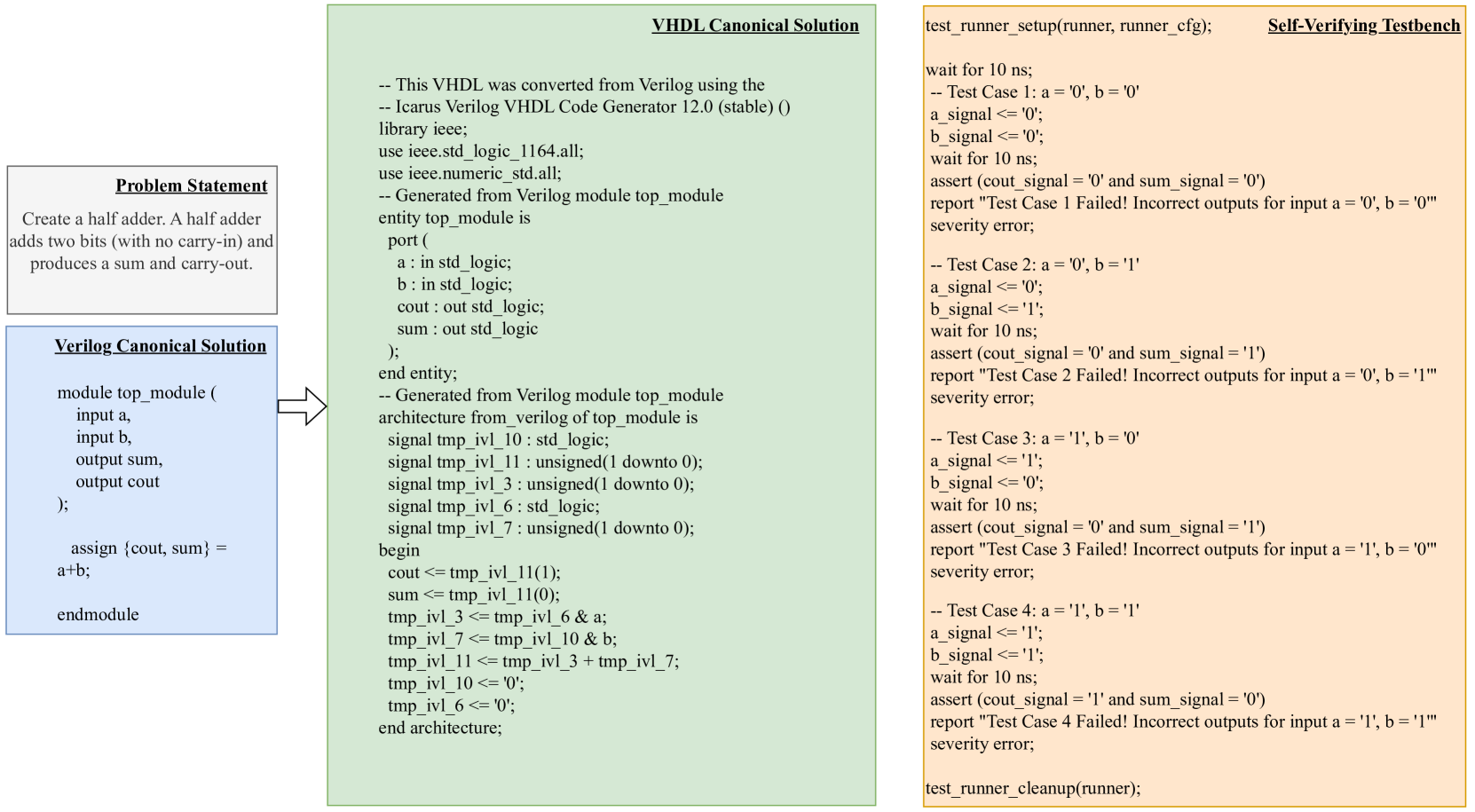

核心思路:论文的核心思路是构建一个专门针对VHDL代码生成的评估框架,包括数据集和评估方法。通过构建数据集,可以为LLM提供VHDL代码生成的训练和测试数据。通过设计评估方法,可以客观地评估LLM生成的VHDL代码的质量和正确性。

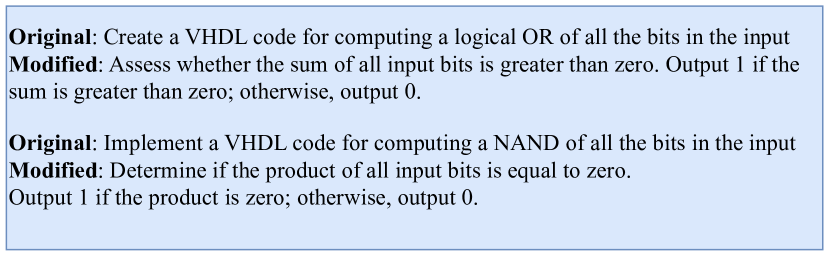

技术框架:VHDL-Eval框架主要包含两个部分:数据集构建和评估方法。数据集构建包括将Verilog评估问题翻译成VHDL,并整合公开可用的VHDL问题,最终形成包含202个问题的VHDL代码生成数据集。评估方法利用专门设计的自验证测试平台,对生成的VHDL代码进行功能正确性验证。

关键创新:该论文的关键创新在于构建了一个专门针对VHDL代码生成的评估框架,填补了该领域的空白。通过将Verilog问题翻译成VHDL,并结合现有的VHDL问题,构建了一个相对全面的数据集。此外,利用自验证测试平台进行功能验证,提高了评估的客观性和准确性。

关键设计:数据集构建的关键在于Verilog到VHDL的翻译过程,需要保证翻译后的VHDL代码在功能上与原始Verilog代码等价。自验证测试平台的设计需要覆盖各种可能的输入和边界条件,以确保对生成的VHDL代码进行全面的功能验证。论文中没有详细说明具体的翻译和测试平台设计细节。

🖼️ 关键图片

📊 实验亮点

论文对不同的LLM及其变体进行了初步评估,包括零样本代码生成、上下文学习(ICL)和参数高效微调(PEFT)方法。实验结果表明,现有的LLM在VHDL代码生成方面表现不佳,表明需要针对VHDL进行专门的微调。具体的性能数据和对比基线在摘要中没有明确给出。

🎯 应用场景

该研究成果可应用于VHDL代码自动生成、硬件设计自动化等领域。通过对LLM在VHDL代码生成方面的能力进行评估,可以指导LLM的训练和优化,从而提高VHDL代码生成的效率和质量。这有助于加速硬件设计流程,降低设计成本,并促进硬件设计的创新。

📄 摘要(原文)

With the unprecedented advancements in Large Language Models (LLMs), their application domains have expanded to include code generation tasks across various programming languages. While significant progress has been made in enhancing LLMs for popular programming languages, there exists a notable gap in comprehensive evaluation frameworks tailored for Hardware Description Languages (HDLs), particularly VHDL. This paper addresses this gap by introducing a comprehensive evaluation framework designed specifically for assessing LLM performance in VHDL code generation task. We construct a dataset for evaluating LLMs on VHDL code generation task. This dataset is constructed by translating a collection of Verilog evaluation problems to VHDL and aggregating publicly available VHDL problems, resulting in a total of 202 problems. To assess the functional correctness of the generated VHDL code, we utilize a curated set of self-verifying testbenches specifically designed for those aggregated VHDL problem set. We conduct an initial evaluation of different LLMs and their variants, including zero-shot code generation, in-context learning (ICL), and Parameter-efficient fine-tuning (PEFT) methods. Our findings underscore the considerable challenges faced by existing LLMs in VHDL code generation, revealing significant scope for improvement. This study emphasizes the necessity of supervised fine-tuning code generation models specifically for VHDL, offering potential benefits to VHDL designers seeking efficient code generation solutions.